17-01 認識結果をUARTでホストFPGAに送る(続き)

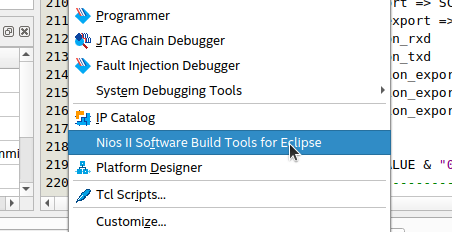

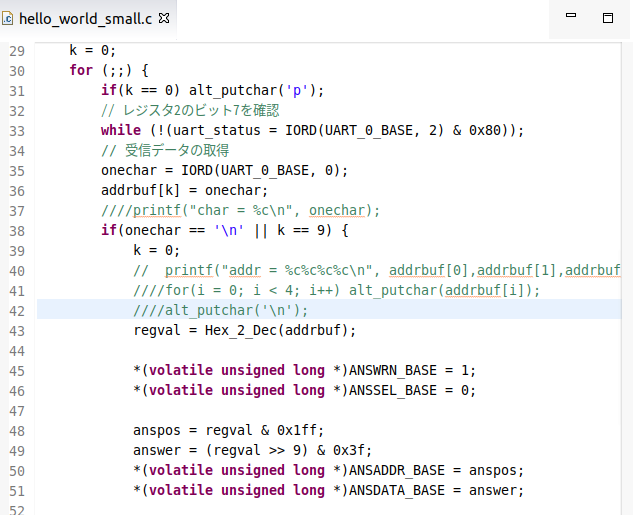

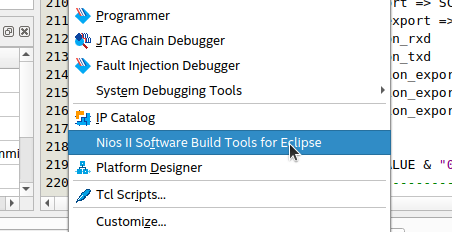

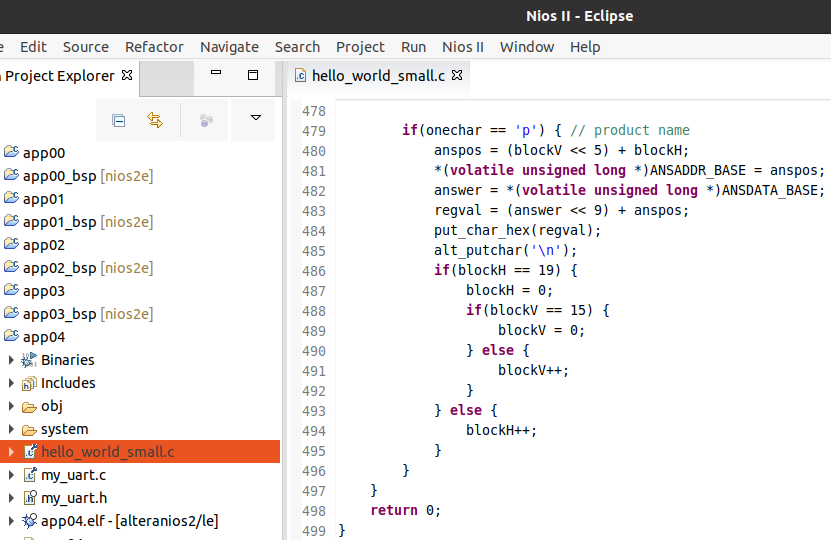

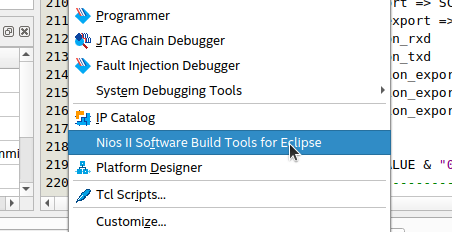

| アプリケーションを新規作成し、hello_world_small.cをこれと置き換えます(UARTライブラリも追加)。その後Build→Run As NiosII Hardware |

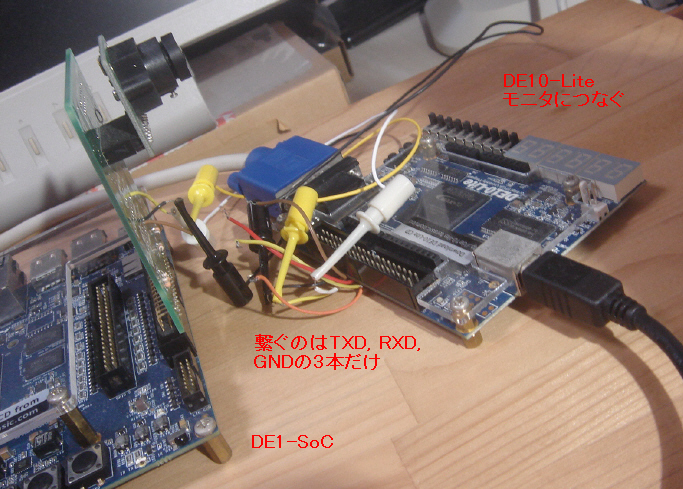

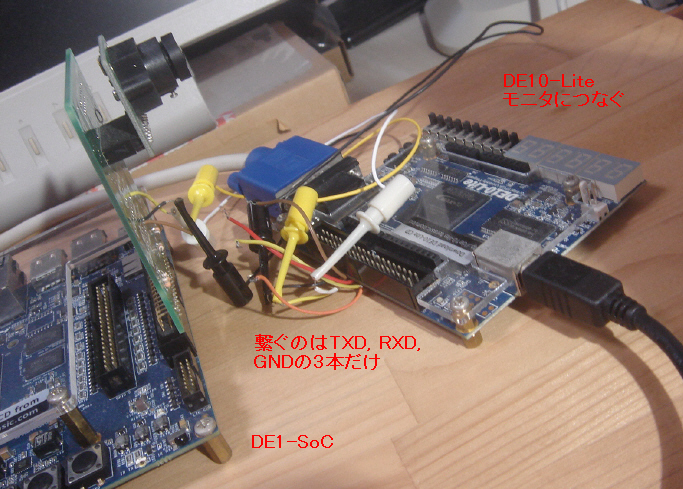

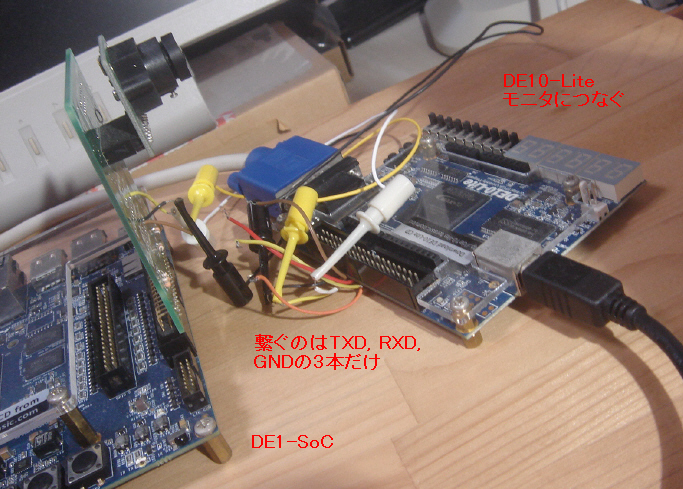

UARTの信号は2つ、TXDとRXDです。次を参考にホストFPGA基板とつなぎます。

| HDLの信号名 |

FPGAのピン |

回路図の信号名 |

DE1-SoCのヘッダ‐ピン番号 |

アダプタ基板(*1) |

| TXD |

AH22 |

GPIO_128 |

JP2-33 |

U1-8 |

| RXD |

AK22 |

GPIO_126 |

JP2-31 |

U2-8 |

(*1)カメラとDE-SoCを繋ぐ基板(次の写真、デジタルフィルタ社製)。U1, U2の8ピンからUART信号が出てくる。 |

| ホストFPGA基板はさしあたりDE10-Liteとします。次の写真のように繋ぎます。 |

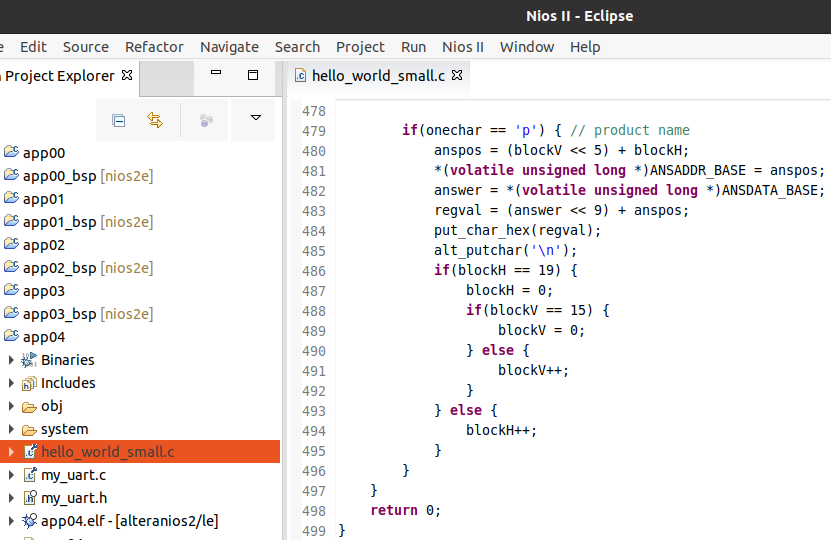

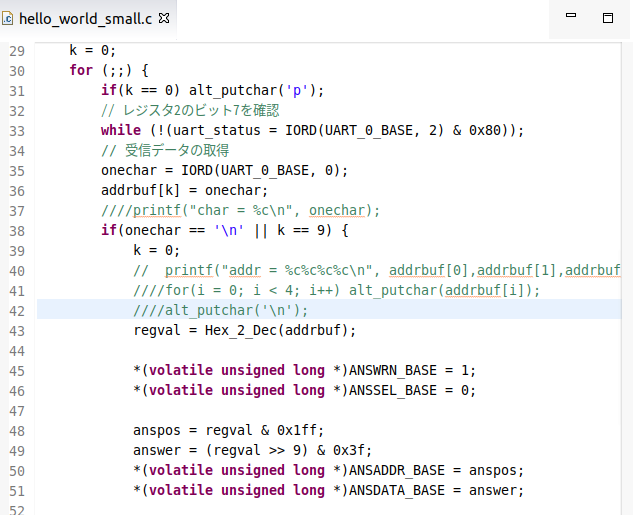

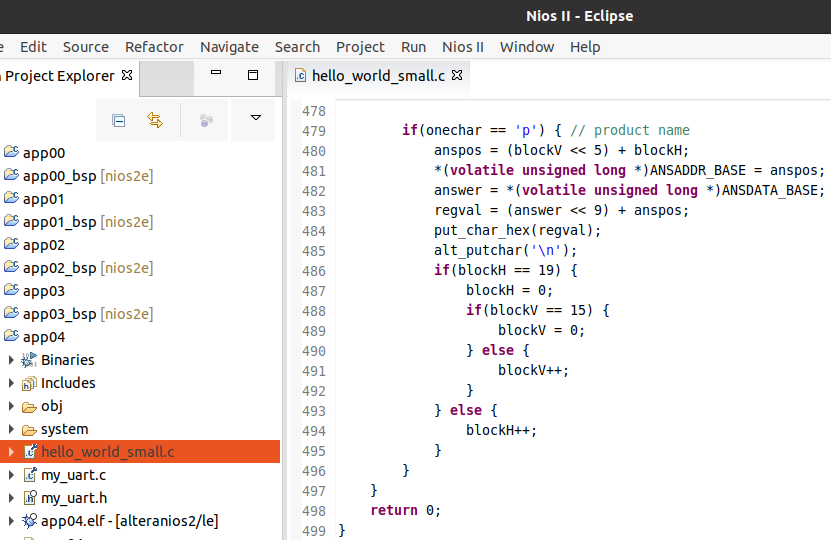

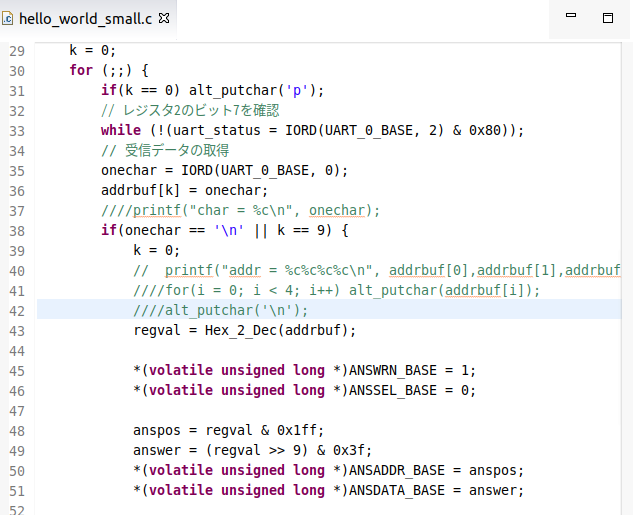

| ホスト(DE10-Lite)側の通信プログラムはこれです。一部を次に示します。 |

| DE1-SoC、DE10-Liteどちらもプログラムして電源を入れると次のようになります。 |

Baud Rateは115200bpsですが情報量が少ないので(ラベル番号と位置情報)、遅延はそれほど感じられません。

現状スレーブ基板は1枚ですが、複数枚で認識を分担し、ホストで認識情報を集中管理することもできます。 |

最初のページへ

目次へ戻る

|