2-03 VHDLを書く

●環境ファイルとテストベンチの役割

前節ではディープラーニングの回路図を書きましたが、本節ではそれをVHDL化します。

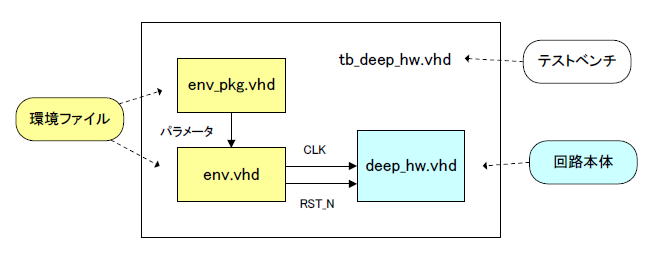

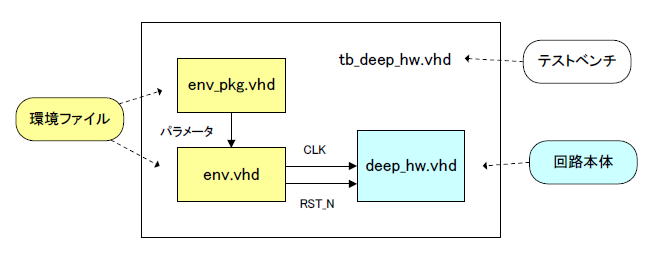

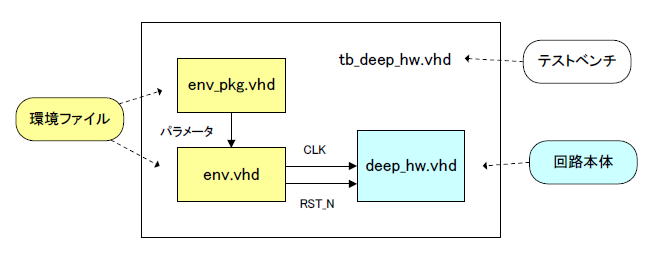

後々シミュレーションを行うことを鑑み、「回路本体」に加えて「環境ファイル」と「テストベンチ」もVHDLで記述します。図2‐16に示すように、環境ファイルはクロックなどの信号を回路本体に供給し、テストベンチは環境ファイルと回路本体をつなぎます。 |

図2‐16 環境ファイルはシミュレーション用の信号発生器

●VHDLファイルの階層構造

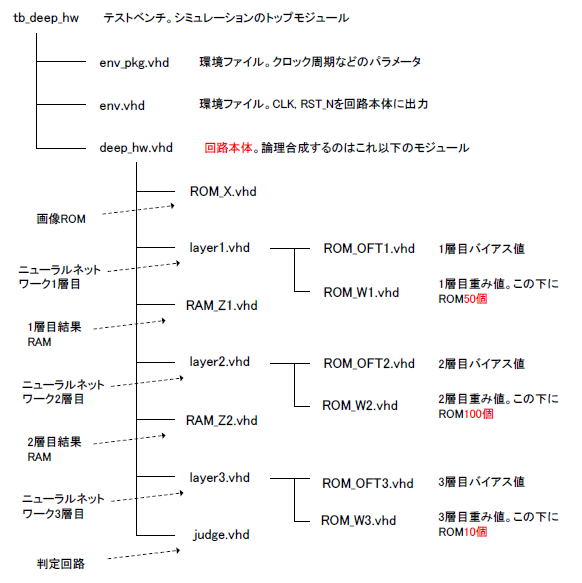

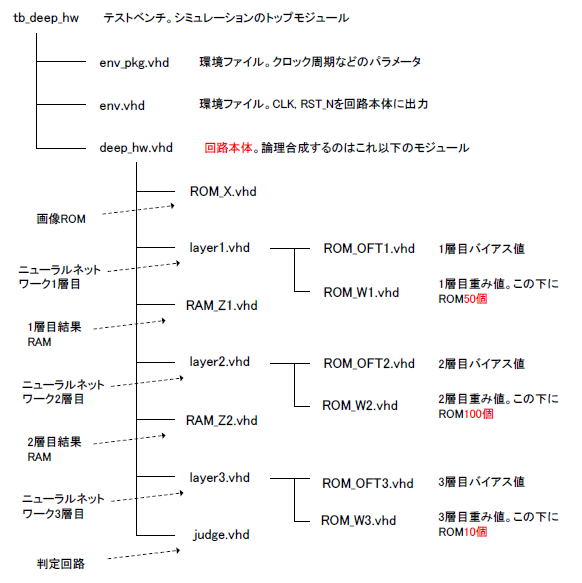

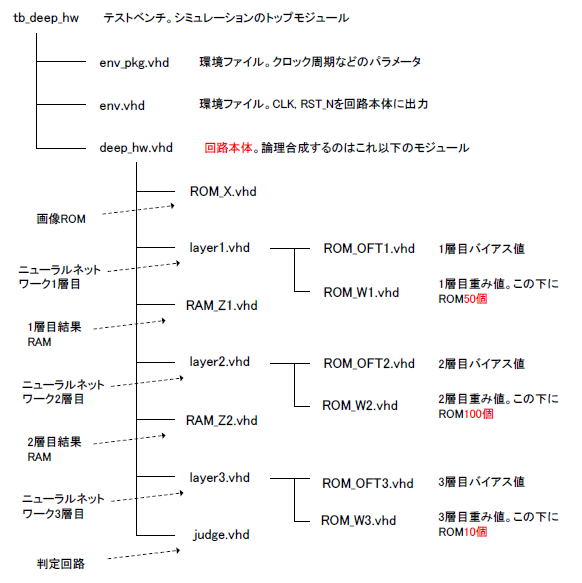

図2‐17はVHDLファイルの構成です(ここにそれらのアーカイブ)。deep_hwは回路本体のトップモジュール、その下にニューラルネットワークの各層layer1〜3があります。

layer1〜3の下にはそれぞれバイアスを格納するROM_OFT1〜3や、重みの値を格納するROM_W1〜3があります。

ROM_W1〜3は多数のROMを一つにまとめ上げたものなので、それらの下にはそれぞれ50、100、10個のROMファイルが存在します(同図では省略)。

ROM_X(画像ROM)に格納された画像データは1層目layer1に入力されます。

1層目と2層目の間にRAM_Z1、2層目と3層目の間にRAM_Z2があります。それらによってデータの受け渡しが各層の間で行われます。

3層目layer3の出力は判定回路judgeに入力され、推論結果の判定が行われます。 |

図2‐17 このような階層構造。論理シミュレーションの際は下の階層からコンパイルする

●画像ROMアドレスを生成するカウンタの部分

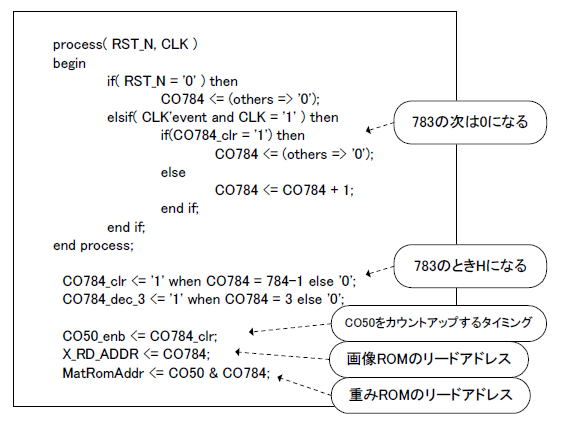

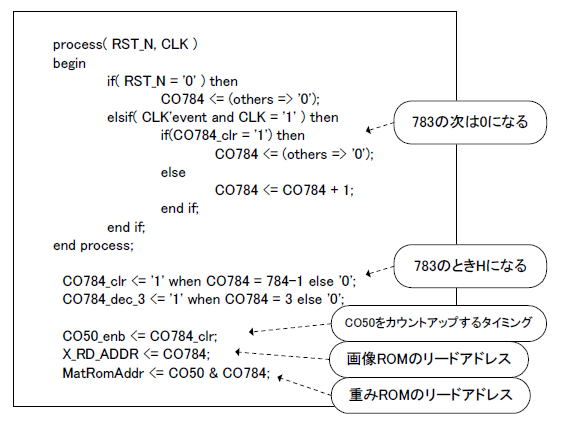

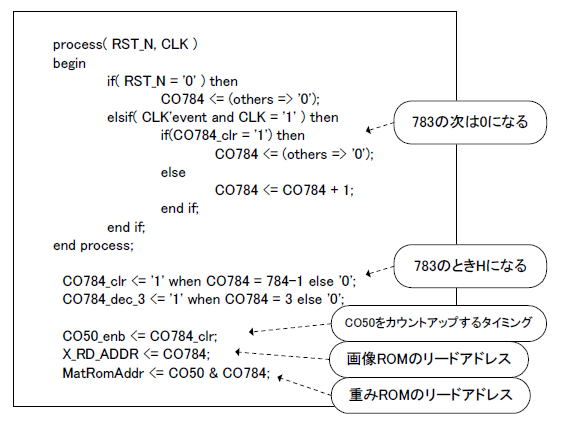

図2‐03の回路図をVHDLで記述するとリスト2‐01のようになります(784進カウンタ)。

CO784=783のときにCO784_clrがHになり、その次のサイクルでCO784=0となります。

またこのカウンタCO784は画像ROMのリードアドレス、重みROMのリードアドレスの一部になります。 |

リスト2‐01 784進カウンタのVHDL (layer1.vhd)

●重みROMアドレスの上位ビットを生成するカウンタの部分

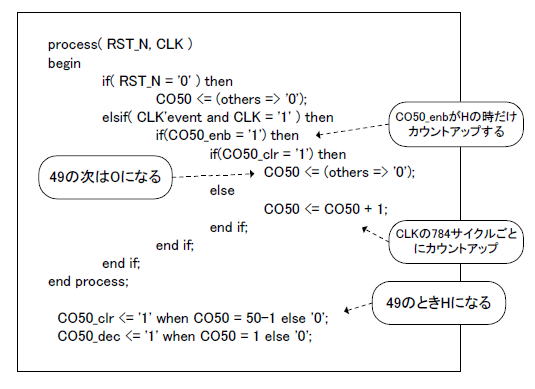

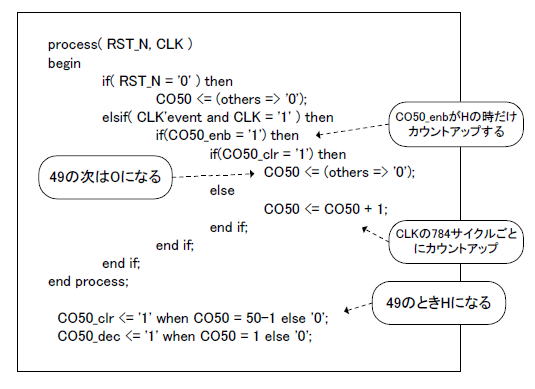

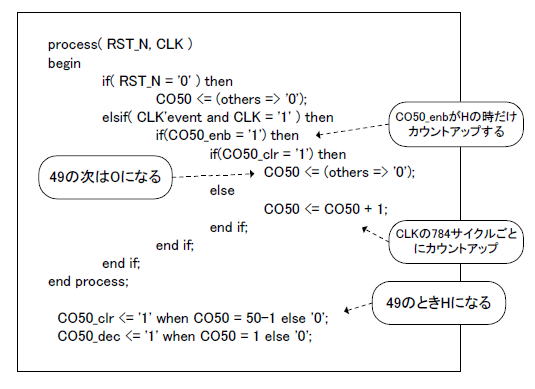

図2‐04の回路図をVHDLで記述するとリスト2‐02のようになります(50進カウンタ)。

重みROMアドレスの下位ビットはCO784で生成しますが、上位ビットはCO50で生成します。

CO50_enbはリスト2‐01に示すように、CO784が最大値(783)になる時だけHになります。すなわち。CO50はCLKの784サイクルごとにカウントアップします。

CO50=49のときにCO50_clrがHになり、その次のサイクルでCO50=0となります。 |

リスト2‐02 50進カウンタのVHDL (layer1.vhd)

次のページへ

目次へ戻る

|