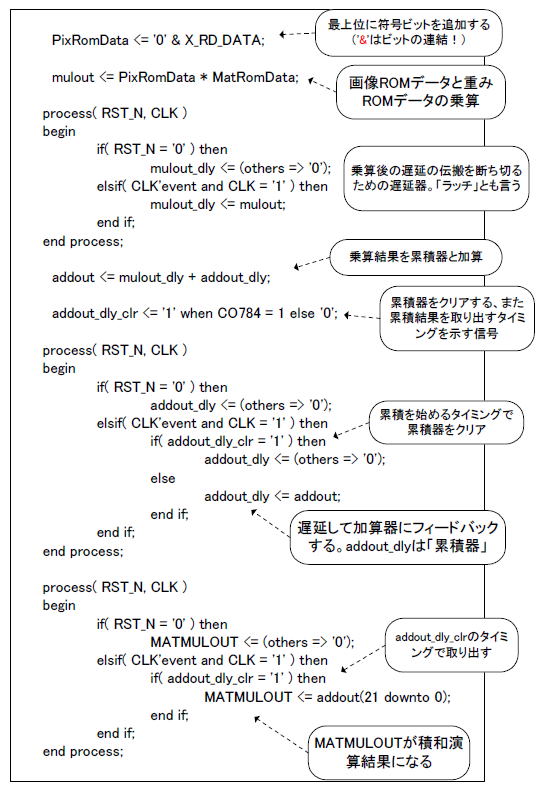

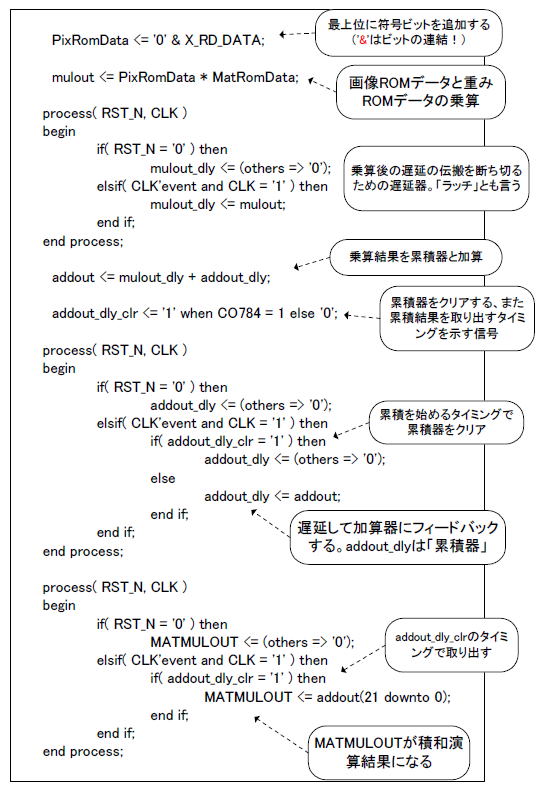

リスト2‐03 積和演算のVHDL (layer1.vhd)

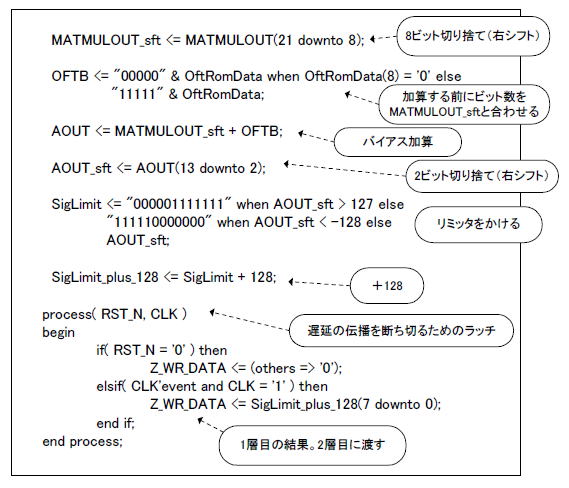

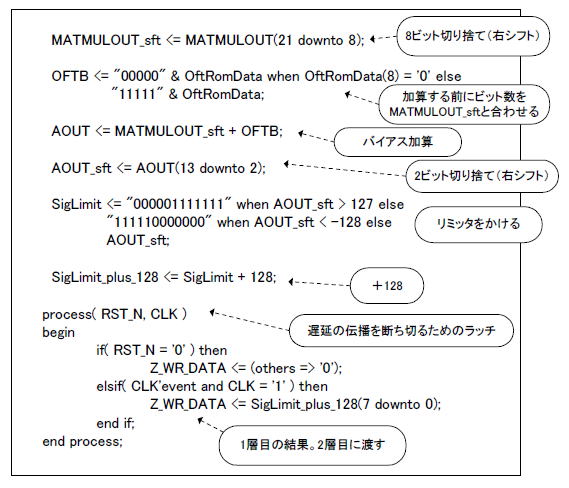

リスト2‐04 バイアス加算→疑似シグモイド関数のVHDL (layer1.vhd)

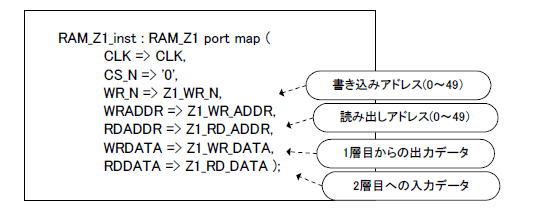

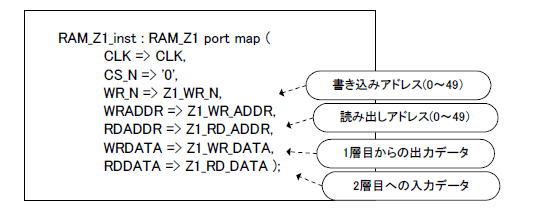

リスト2‐05 RAMを介して次の層へデータを渡す (deep_hw.vhd)

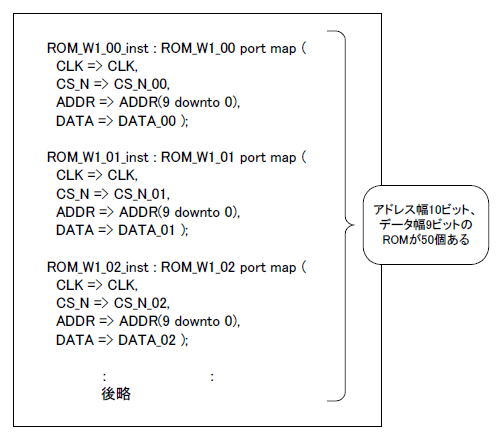

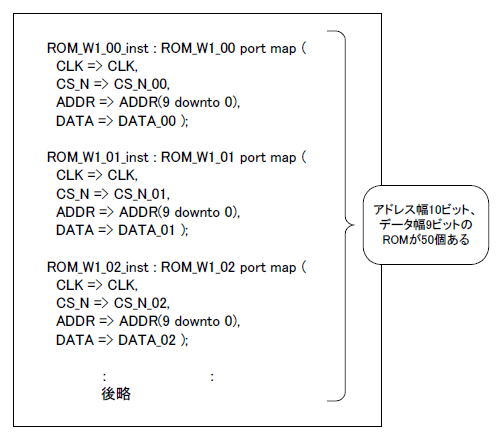

リスト2‐06 ROM_W1は50個のROMを一つにまとめたもの (ROM_W1.vhd) 最初のページへ 目次へ戻る |

リスト2‐03 積和演算のVHDL (layer1.vhd)

リスト2‐04 バイアス加算→疑似シグモイド関数のVHDL (layer1.vhd)

リスト2‐05 RAMを介して次の層へデータを渡す (deep_hw.vhd)

リスト2‐06 ROM_W1は50個のROMを一つにまとめたもの (ROM_W1.vhd) 最初のページへ 目次へ戻る |