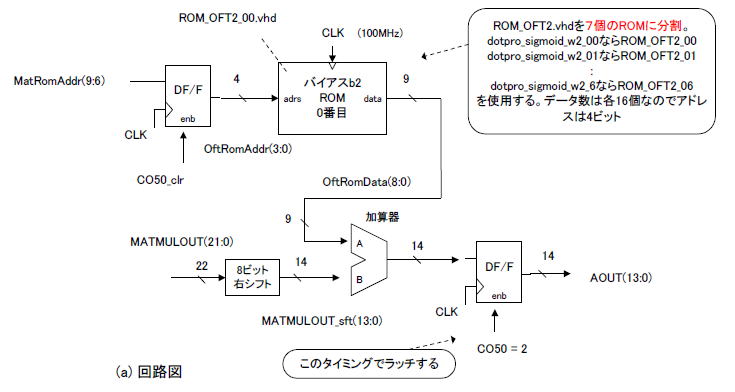

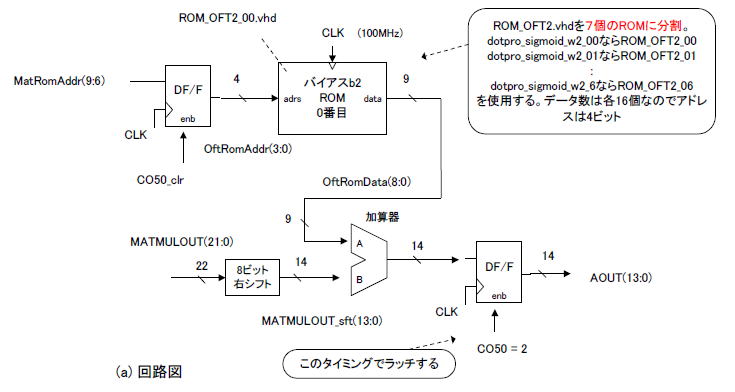

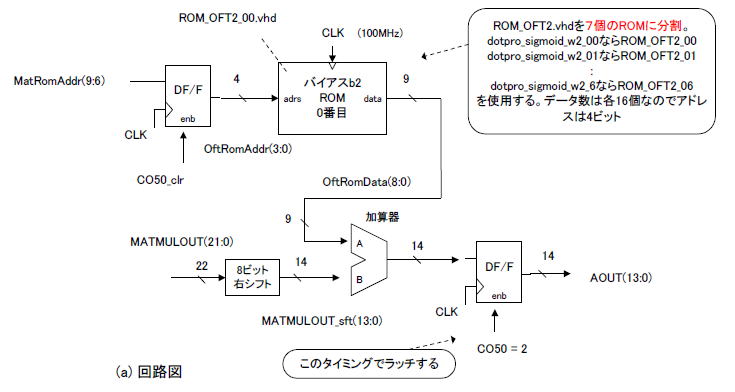

●バイアスを加算する部分の回路図とタイムチャート

図3-21のマルチプレクサ以降の回路図は基本的に図2-05、図2-06と同じですが、バイアスOftRomDataを足す部分は違ってくるので説明します。

図3-24(a)にその部分の回路図を示します。ROM_OFT2.vhdには100個のバイアス値が入っていましたが、それを7個のROMに分割します(ROM_OFT2_00〜06)。それぞれ16個のバイアス値が入っています。

ROM_OFT2_00〜06からのデータはdotpro_sigmoid_w2_00〜06に入力され、バイアス値が加算されます。 |

図3-24 バイアスを加算する部分

図3-24(b)にタイムチャートを示します。積和演算結果Pnが有効になるのはCO50=2のタイミングです。またバイアスBnが得られるのはCO50=1のタイミングです。したがって加算器の出力をCO50=2のタイミングでラッチすれば正しい結果Anが得られます。

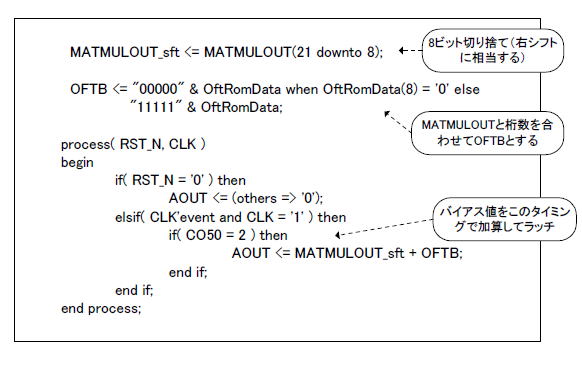

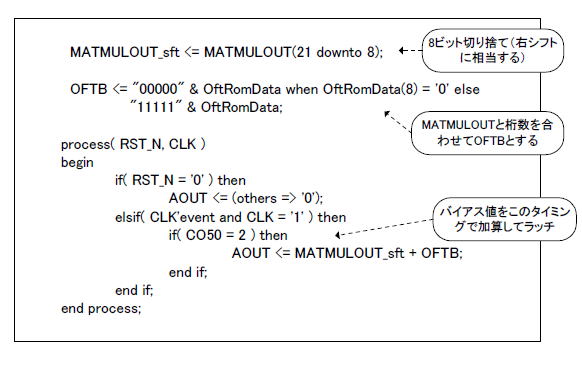

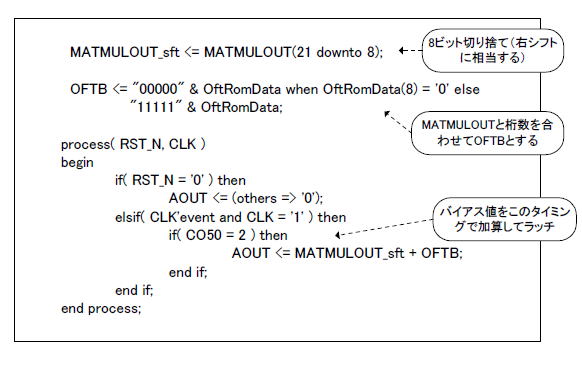

●バイアスを加算する部分のVHDLソース

図3-24(a)をVHDLで記述するとリスト3-21のようになります。積和演算結果を8ビットシフトした後、バイアス値を加算し、それをCO50=2のタイミングでラッチしています。 |

リスト3-21 バイアスを加算する部分

次のページへ

目次へ戻る

|