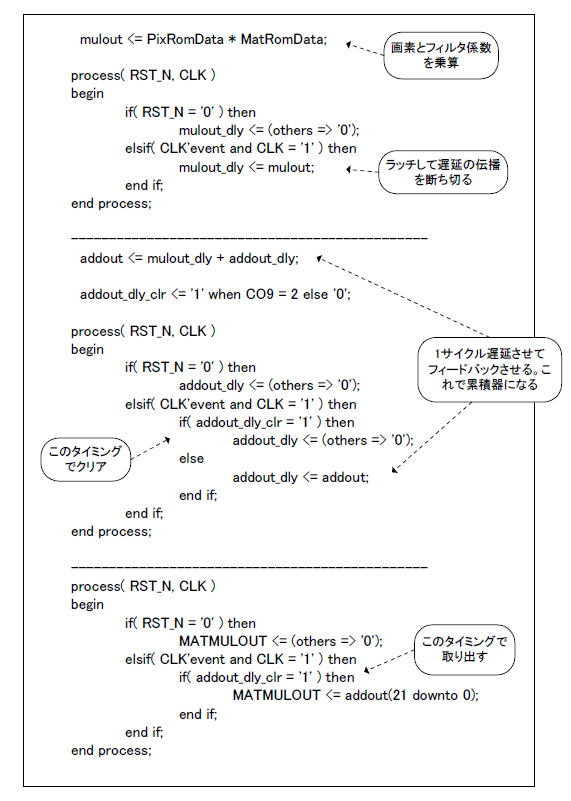

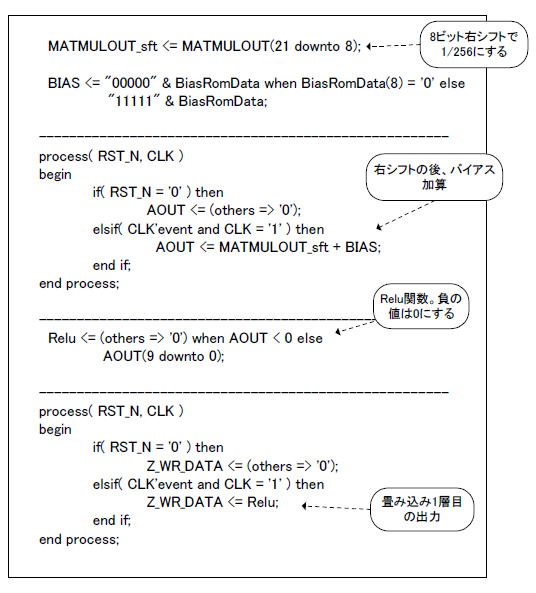

●積和演算回路

リスト6-03はこの回路図の部分です。

muloutは画素データとフィルタ係数を掛け合わせたもので、こう記述すると論理合成時に乗算器に割り当てられます。乗算によりCLKのエッジに対する遅延が大きくなるので、同リストのようにラッチしてmulout_dlyとします。1サイクル余計に遅延しますが、CLKのエッジに対する遅延は少なくなります。

mulout_dlyは加算器に入力されます。そして加算結果addoutを1サイクル遅延させたaddout_dlyをもう一方の入力とすれば、累積器を構成できます。

加算結果addoutをCO9=2のタイミング(addout_dly_clr)でラッチすれば積和結果MATMULOUTを取り出すことが出来ます。 |