コラム142 CMOSカメラからの動画をリアルタイムに推論させる仕組み

この写真ではCMOSカメラの動画をVGAに映しつつ推論を行い、その結果をVGAに上書きしています。本コラムではまずカメラ動画をリアルタイムにディープラーニング回路に入力する仕組みを解説します。

●動画と推論結果、両方VGAに映すには・・・

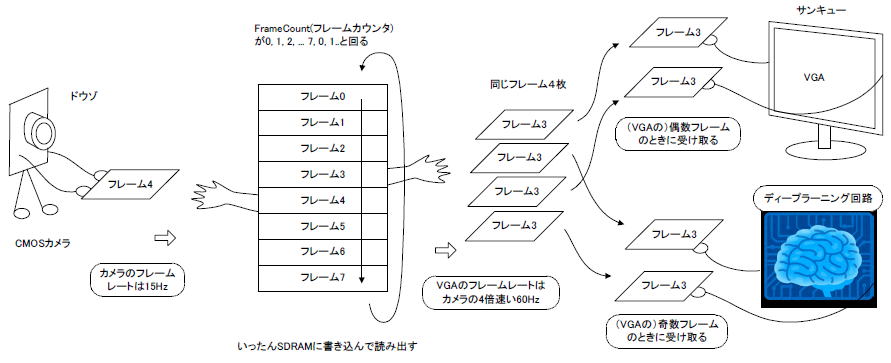

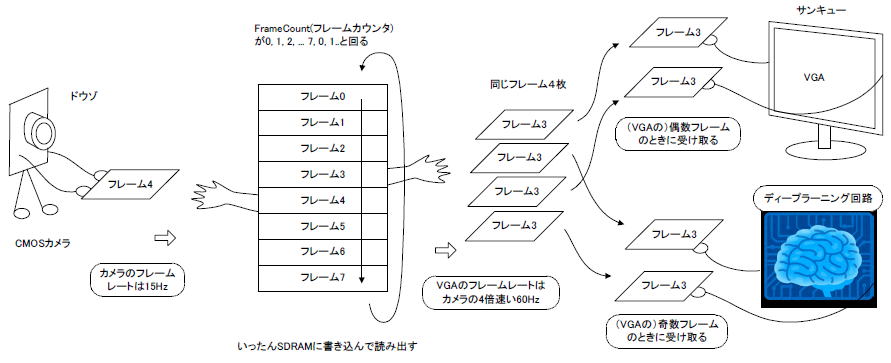

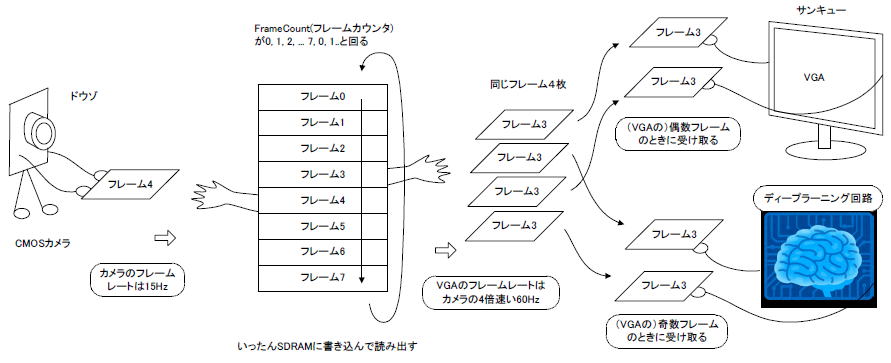

CMOSカメラとVGAは垂直同期周波数が違うのでSDRAMでこのように同期をとります。周波数が4倍(60Hz/15Hz)になるので、VGAは同じフレームを4枚受け取ります。

単にカメラ動画を映すだけならこれで良いのですが、推論結果を動画に重ね書きする必要があります。そのためには図14‐10のようにVGA→ディープラーニング回路→VGA→ディープラーニング回路、と代わりばんこにフレームを送ります。 |

図14‐10 代わりばんこにフレームを渡す

●VGAを細かいブロックに分割する

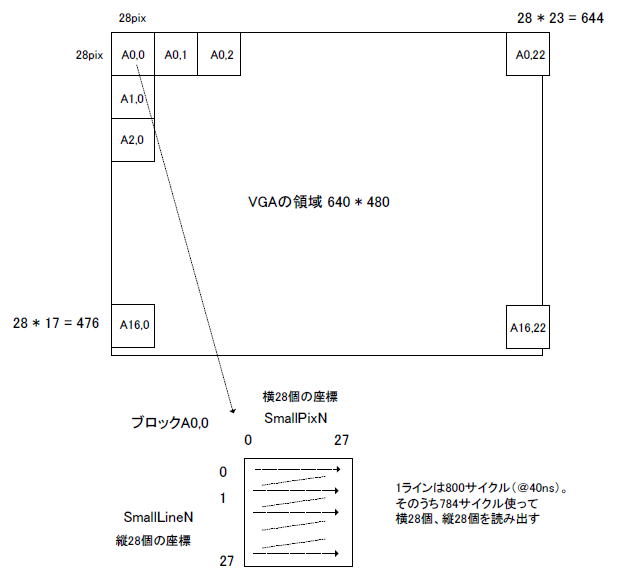

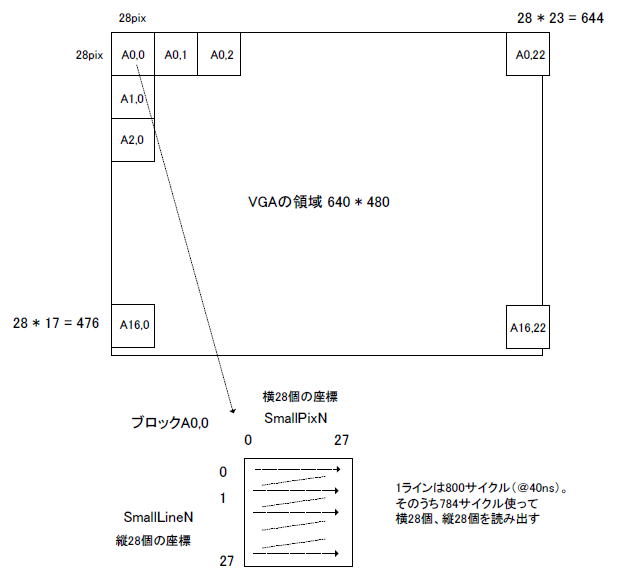

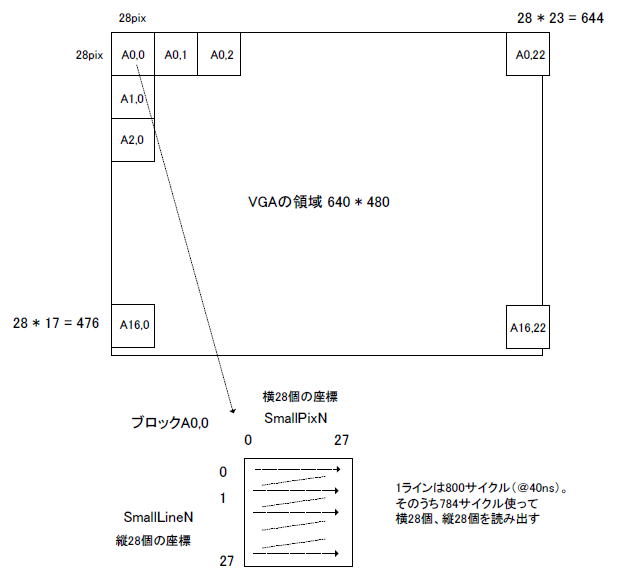

VGAなので各フレームは640×480画素ですが、ディープラーニング回路は28×28画素を推論するように作ってあります。したがって図14‐11のように横23個、縦17個のブロックに分割します。

左上のブロックA0,0は28x28 = 784画素あり、それらが同図下にあるように走査します。座標の横軸をSmallPixN、縦軸をSmallLineNとしてそれらのタイミングを見てみましょう。 |

図14-11 ブロック分割とブロック内走査法

●水平同期で1ブロック、垂直同期で23×17ブロック読む

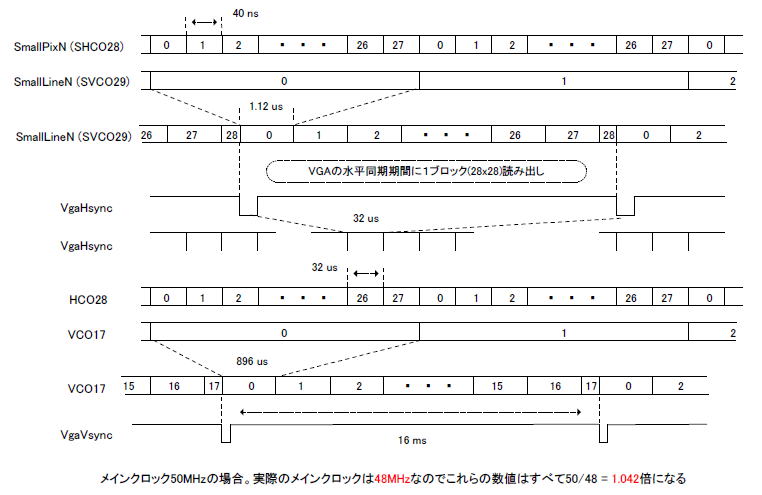

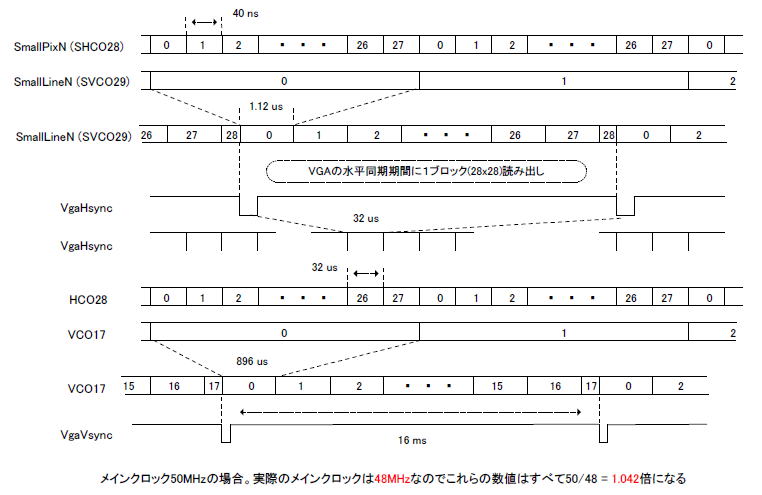

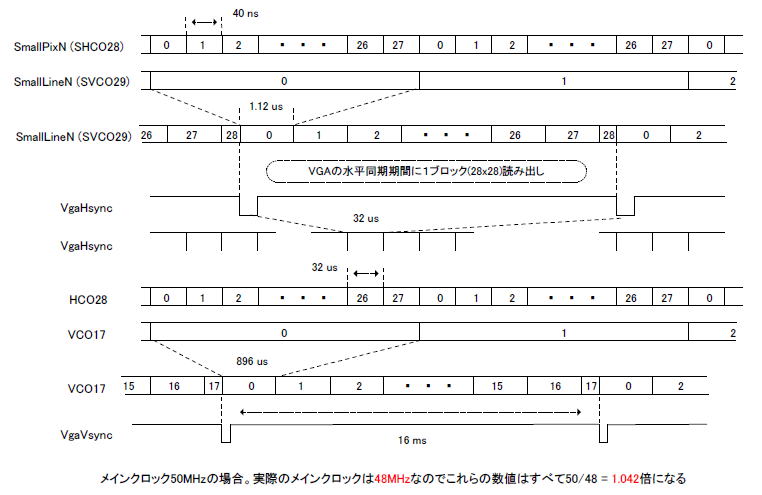

図14‐12にタイムチャートを示します。VHDLファイル内ではSmallPixNはSHCO28,

SmallLineNはSVCO29という信号になります。これらを画像の横、縦のアドレスとすれば、図14‐11の下の図のような走査法で画素を取り出せます。各画素が出てくるサイクルは40nsになります。

VGAの水平同期信号の周期は32usなので、その期間のサイクル数は32us/40ns = 800です。したがってVGAの水平同期期間(32us)の間に1ブロック784画素すべてを読み出すことができます。また800-784 = 16サイクル余るので、SVCO29は28まで進んでから0に戻ります。

HCO28は水平同期信号VgaHsyncを数えたもので、0から27まで行ったら0に戻ります。1ラインで1ブロック読むので時間的には28ブロック読めるのですが、図14‐11の上の図に示すようにブロックは横に23個しかありません。したがってHCO28が0~22の期間が有効で、23~27の期間は無効になります。

VCO17が0の期間はブロックA0,0~A0,22まで、横に23ブロック読みます。1の期間はブロックA1,0~A1,22まで、2の期間はブロックA2,0~A2,22まで、・・・16の期間はブロックA16,0~A16,22まで読みます。

同図のようにVCO17は32us x 28 = 896usでインクリメントします。ブロックは縦に17個あるので896us x 17= 15.232msとなり、VGAの垂直同期期間(16ms)以内に23×17ブロックすべてを読み出すことができます。 |

図14-12 ブロック読み出しのタイムチャート

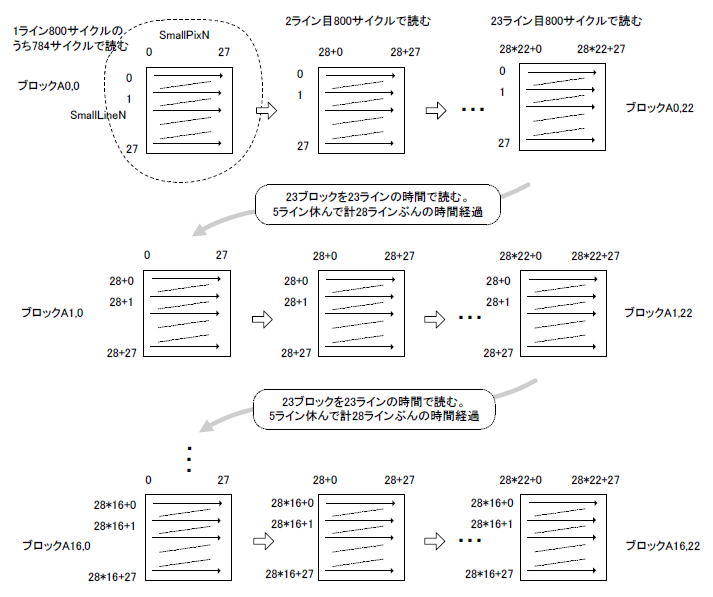

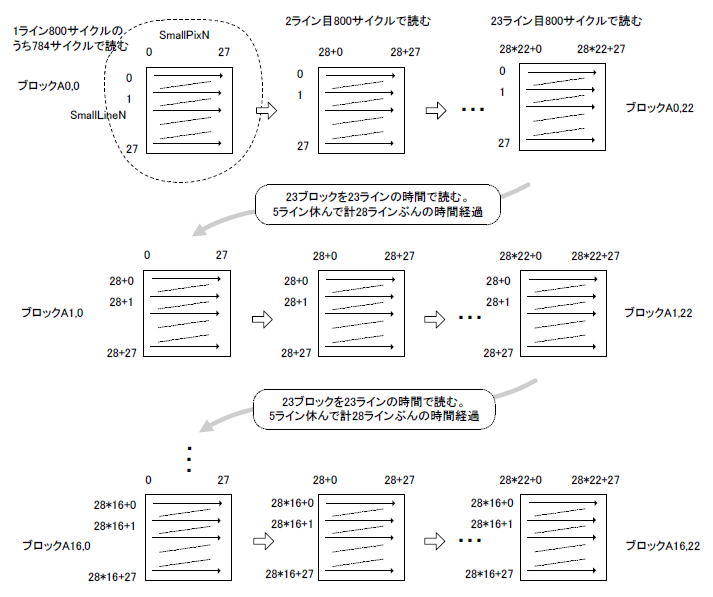

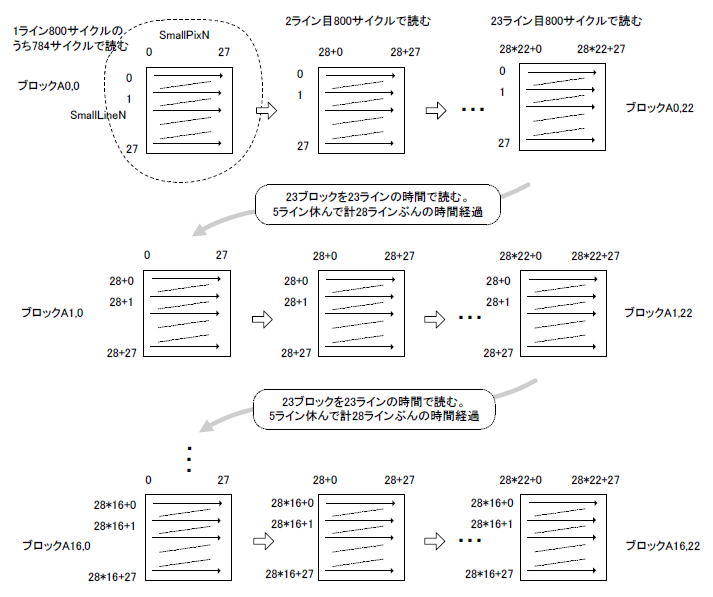

●オフセットを加算すれば各ブロックが読める

SmallPixN, SmallLineNはブロックA0,0を読み出すときに使用します。他のブロックはどうするのかというと、図14‐13のようにSmallPixN, SmallLineNに適宜オフセットを加算します。このようなシーケンスでSDRAMにアドレスを与えて読み出し、ディープラーニングの回路に入力します。 |

図14-13 各ブロックの画素がSDRAMのどこにあるかを考える

目次へ戻る |