コラム143 推論結果をVGAに重ね書きさせる仕組み

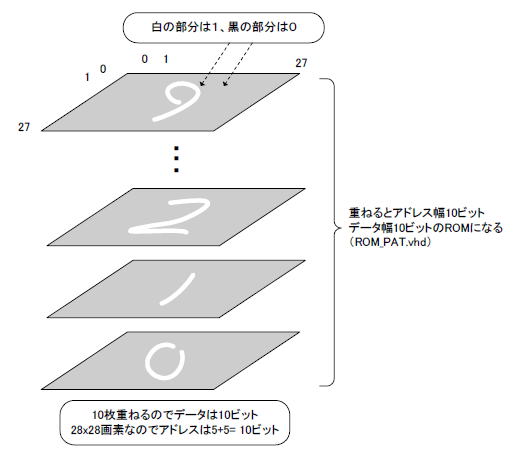

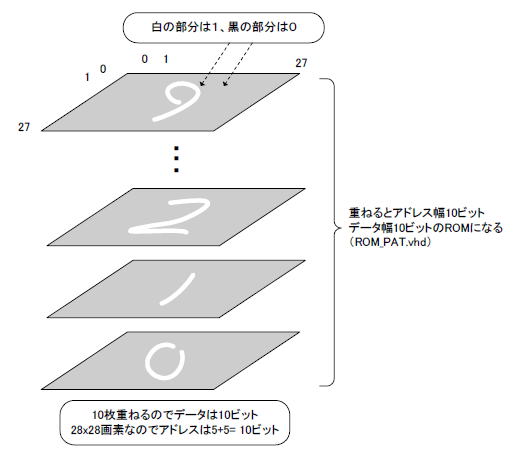

図14‐20 薄いROMを重ねるイメージ

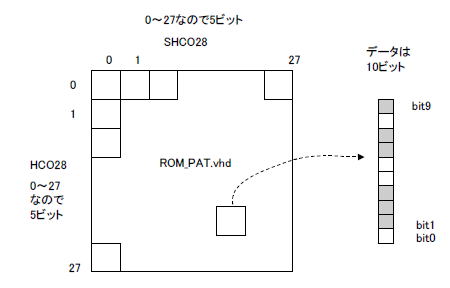

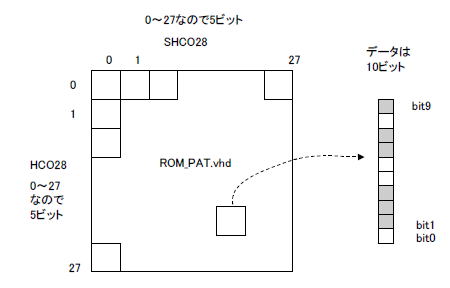

図14-21 28×28×10ビット

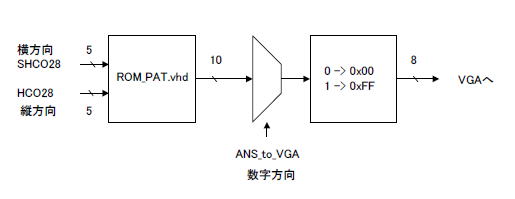

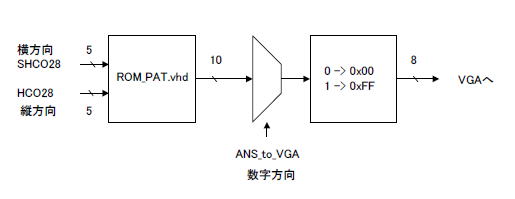

図14-22 数字パターンを選んで表示

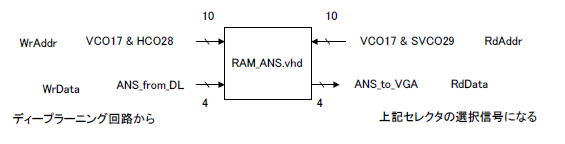

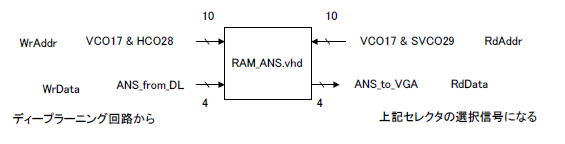

図14-23 推論結果をいったんRAMに書き込んで読み出す 目次へ戻る |

||||||||||||||||

コラム143 推論結果をVGAに重ね書きさせる仕組み

図14‐20 薄いROMを重ねるイメージ

図14-21 28×28×10ビット

図14-22 数字パターンを選んで表示

図14-23 推論結果をいったんRAMに書き込んで読み出す 目次へ戻る |

||||||||||||||||