コラム124 メインクロック1サイクル以上の遅延が許される例

DE1-SoCには50MHzのクロックが搭載されています。それをPLLで100MHzに逓倍したものを本システムのメイン・クロックとして使っています。

●多数の信号を一度に加算しているけど大丈夫?

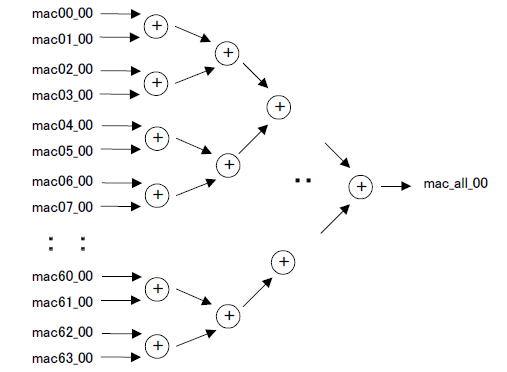

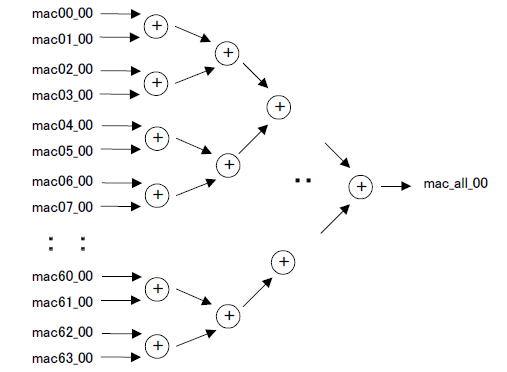

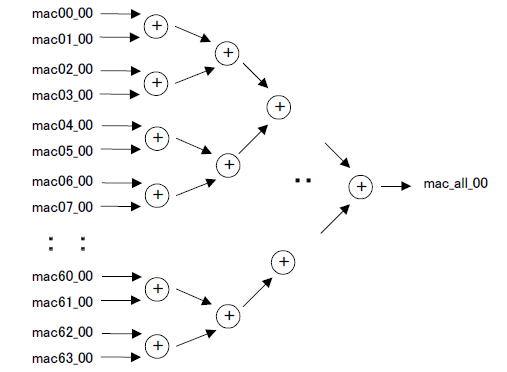

下図は畳み込み6層目のVHDLの一部です。このように64個もの信号を加算してmac_all_00という信号を生成しています。メインクロックの周期は10nsしかありません。こんなに盛大に加算して間に合うでしょうか? |

上図のようなVHDLを論理合成すると下図のような、64チームのトーナメント表のような加算になると思います。夏の甲子園と同じように、3試合勝ってベスト8、優勝するには6試合必要です。加算器1個の遅延を例えば3nsとすると(*1)、3x6

= 18nsとなり、1サイクルでは間に合いません。

(*1)遅延時間はビット数やデバイス特性に依存する。 |

下図はが処理のようすをシミュレーションしたものです。mac00_00〜mac63_00を加算したものがmac_all_00になります。

それの下位ビットを削除したものがtruncate_00、バイアス加算したものがplusBias_00、ReLU処理したものがRelu_00となります。

Relu_00はWRDATAとなり、RAMに書き込まれます。書き込みタイミングはWR_Nの立ち上がりになります。シミュレーションでは60nsもの余裕があることが分かります。

したがってmac_all_00の時点で18ns遅延していたとしても全く問題がないことが分かります。 |

●コンストレインしていないクロックがあるけど大丈夫?

ここで入力クロックをConstrainしましたが、下図を見るとUnconstrainクロックがいくつかあります。コンストレインしなくて大丈夫でしょうか? |

| これらの信号は周期が長く、下図のシミュレーションでは18usと、メインクロックの1000倍以上あります。これらをクロックとして使用した場合、Unconstrainedだと10ns以上遅延する可能性がありますが、それでも全く問題ないことをシミュレーションで確認しているので大丈夫です。 |

| メインクロックの周期が10nsだからといって、何もかもその期間に処理を終えなければならない、ということはありません。やみくもにDF/Fでラッチしてリソースを無駄にしないように気をつけましょう。 |

目次へ戻る |