6‐07 1層目シミュレーションとEXCELの答え合わせ(続き)

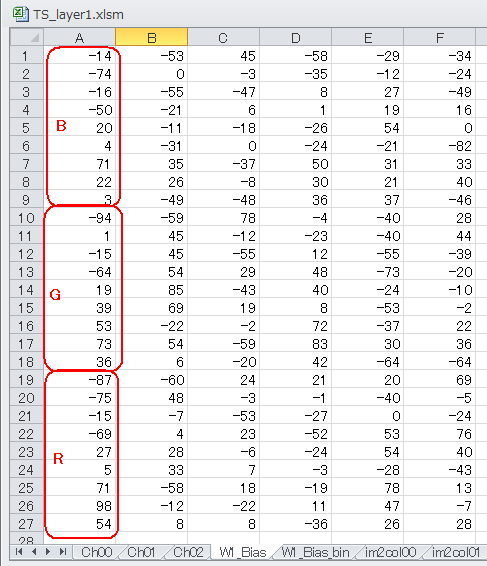

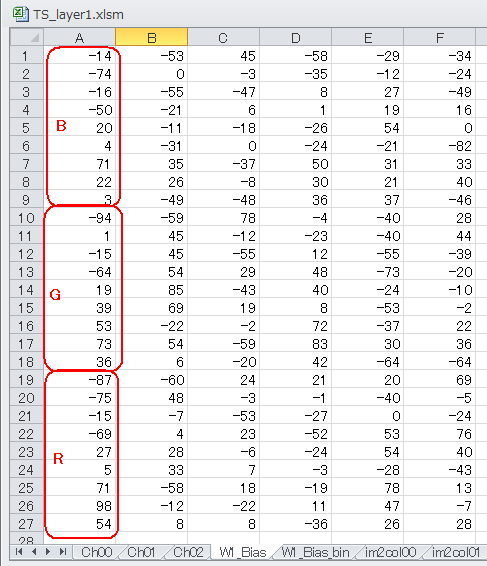

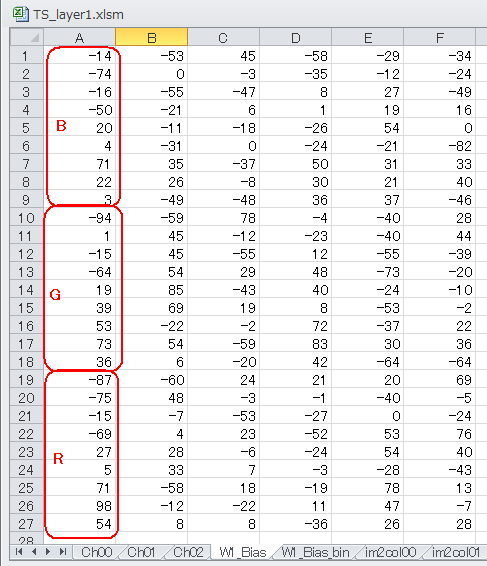

●重み係数はEXCELと合っているか

次は重み係数を見てみましょう。EXCELのW1_Biasシートの左端のRGBに対応する係数は、-87,

-75, -15, -69, 27, 5, 71, 98, 54,,, -94, 1, -15, -64, 19, 39, 53, 73, 36,,,

-14, -74, -16, -50, 20, 4, 71, 22, 3 となっています(BGR -> RGB)。それらと図6‐52のMatRomDataの値を比較して一致を見ます。

入力画素データと重み係数とどちらも一致すれば積和結果も一致するはずです。一致しないならその理由として、RAM/ROM読出しシーケンスのミス、双方のタイミングのずれ等が考えられます。 |

図6-55 W1_Biasシート。上からBGRになっていることに注意

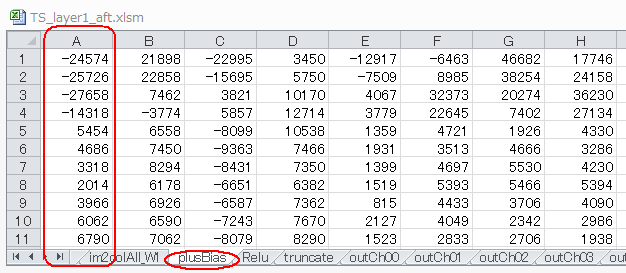

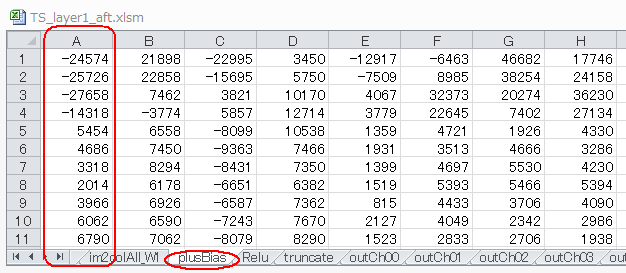

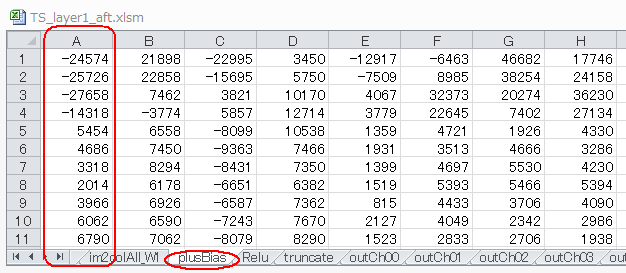

●積和演算の後を見る

図6‐50のmac_00〜15(積和演算器の出力)にはバイアスが加算され、図6‐56(a)のようになります。plusBias_00信号が、EXCELのplusBiasシート(同図(b))のA列に相当します。 |

図6-56(a) バイアス加算(シム)

図6-56(b) バイアス加算(EXCEL)

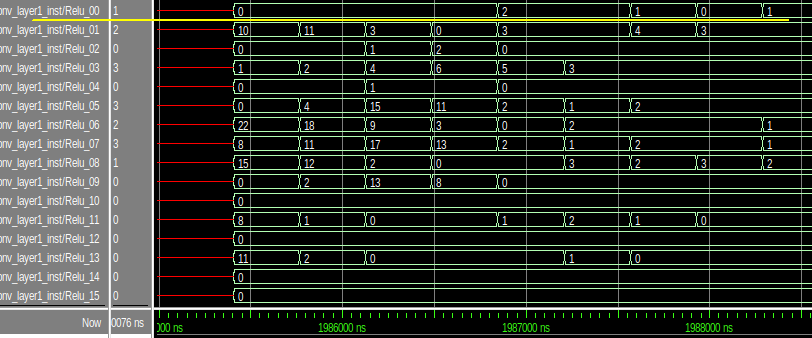

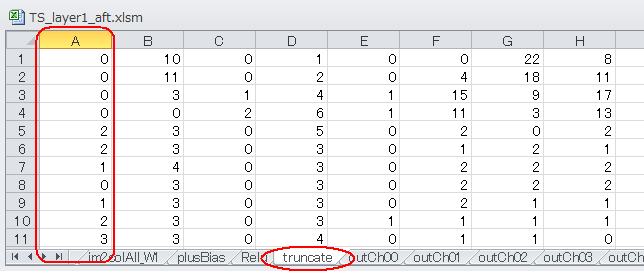

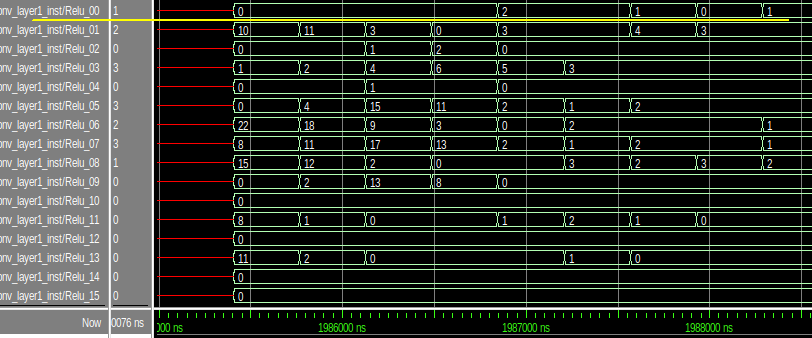

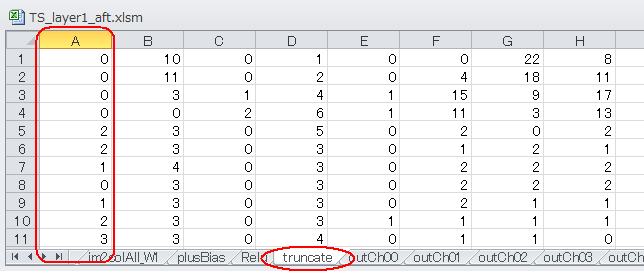

●ビット切り捨て→ReLU(リミッタ込み)

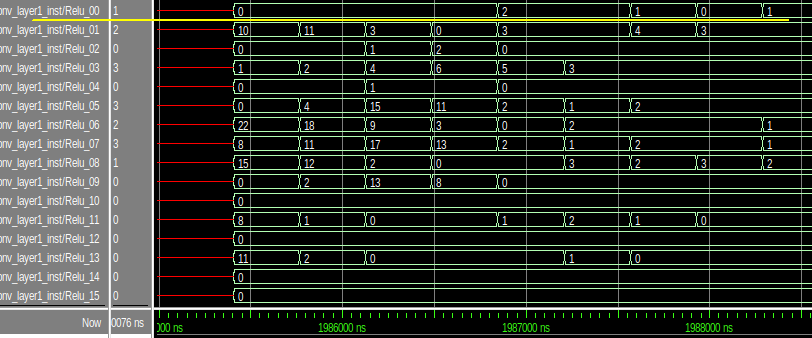

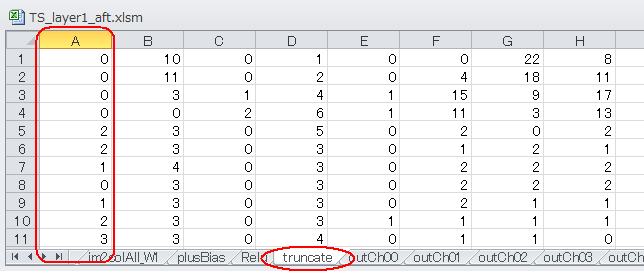

バイアス加算の後、truncate_00〜15(11ビット切り捨て)、Relu00〜15(ReLU関数)を経て1層目の出力となります(図6‐57(a))。またReLUの際、リミッタが施されて値は0〜15(符号なし5ビット)となります。

同図(b)はEXCELのtruncateシートです(*1)。Relu_00信号がA列に相当します。

(*1)EXCELではReLU -> truncateだがHDLではtruncate -> ReLUになっている(その方がFPGAリソースを減らせるので)。順番が違っても結果は同じになる。 |

図6‐57(a) 1層目の出力(シム)

図6‐57(b) 1層目の出力(EXCEL)

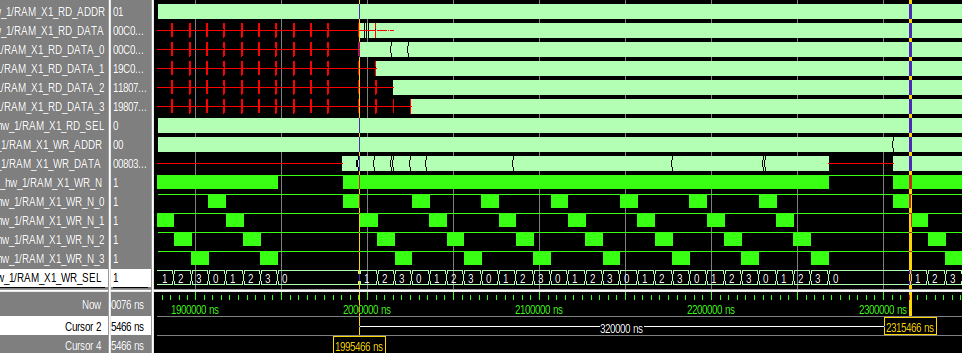

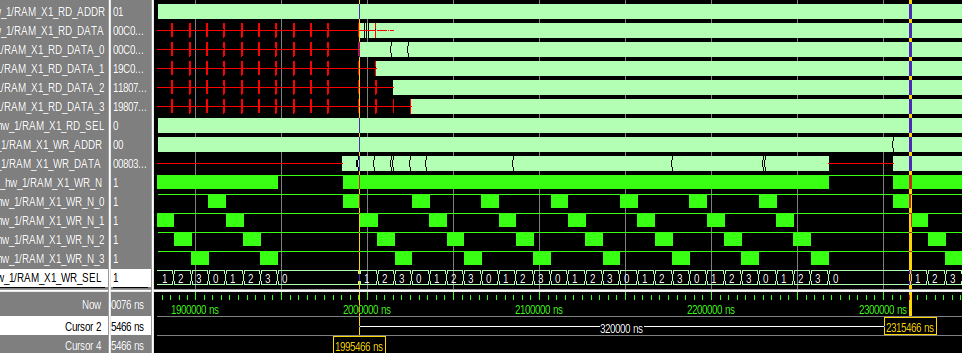

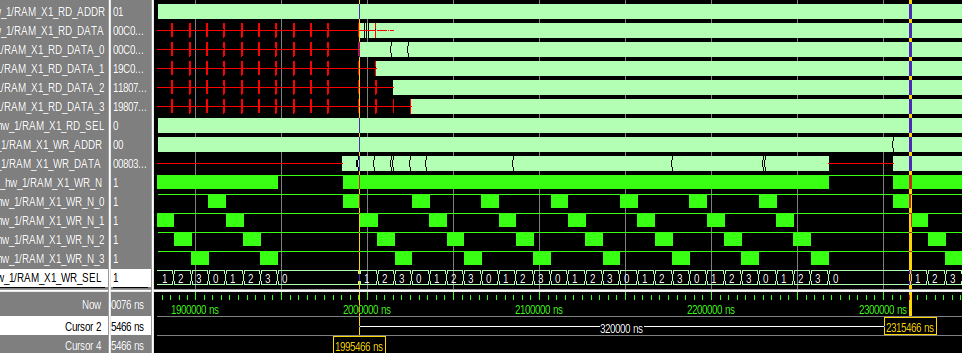

●28x28画素を320usでRAMに書いて2層目へ

図6‐58は1層目の出力RAMの信号です。CNN1ブロックを処理する時間は320us、その時間内にRAM_X1_WR_N_Xが28ラインぶんLになっています。RAM_X1_WR_SELは1ラインごとに0,

1, 2, 3, 0...と遷移し、それに相当するRAM_X1_WR_N_XがLになります(このように書き込む)。 |

図6‐58 RAM_X1にはラインバッファが4つある。順番に書き込む

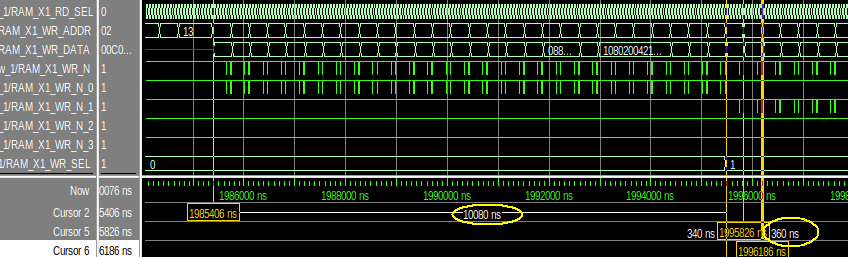

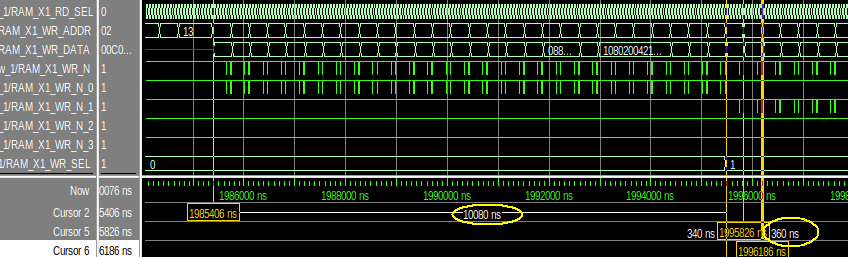

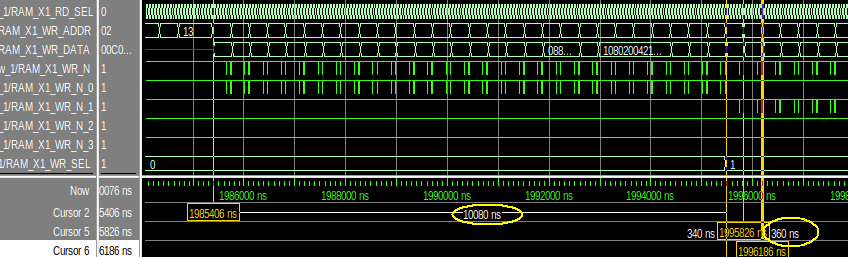

●書き込みタイミングが想定通りになっているか

図6‐59のように1画素書き込むのに360ns、1ライン(28画素)書き込むのに10.08usかかります。このタイムチャート通りになっているか確認しましょう。 |

図6‐59 RAM_X1の書き込みを拡大

最初のページへ

目次へ戻る

|