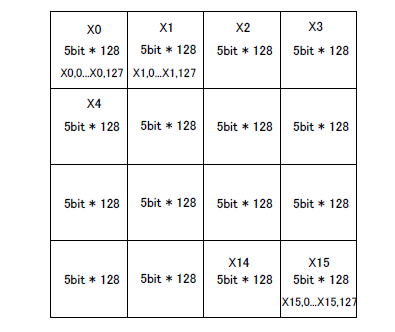

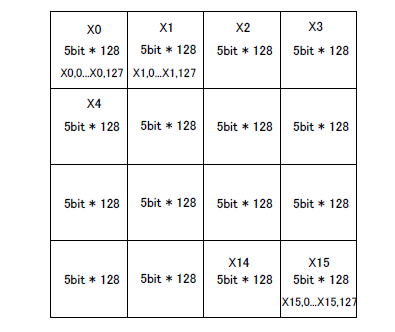

●データ128個×16=2048個を重み係数2048個と積和

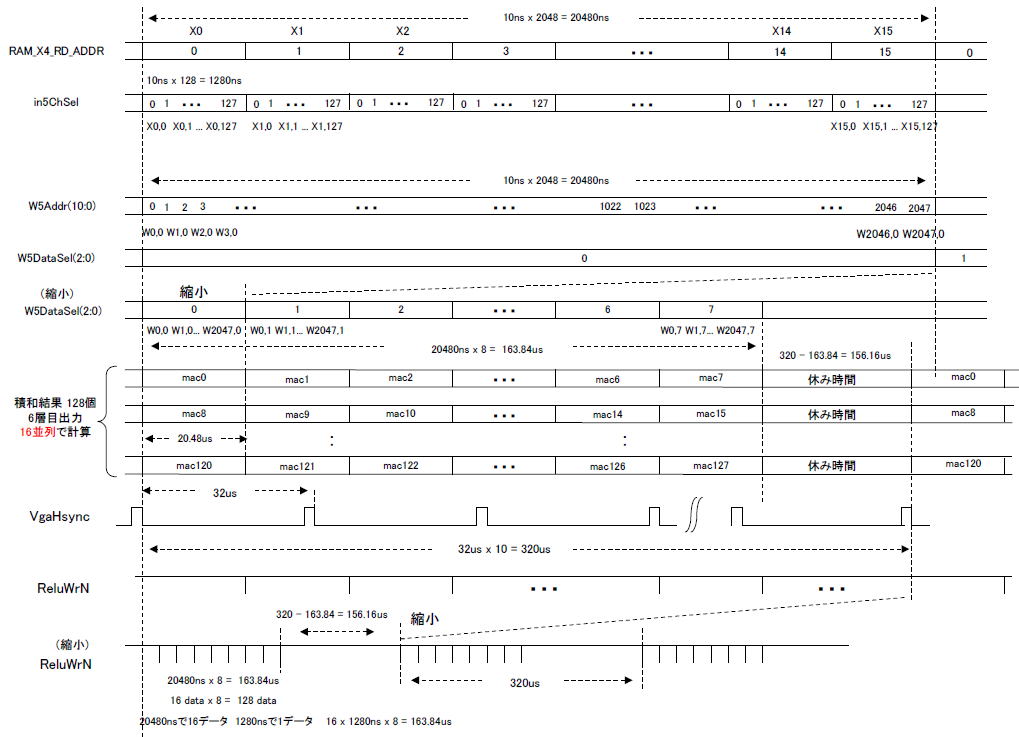

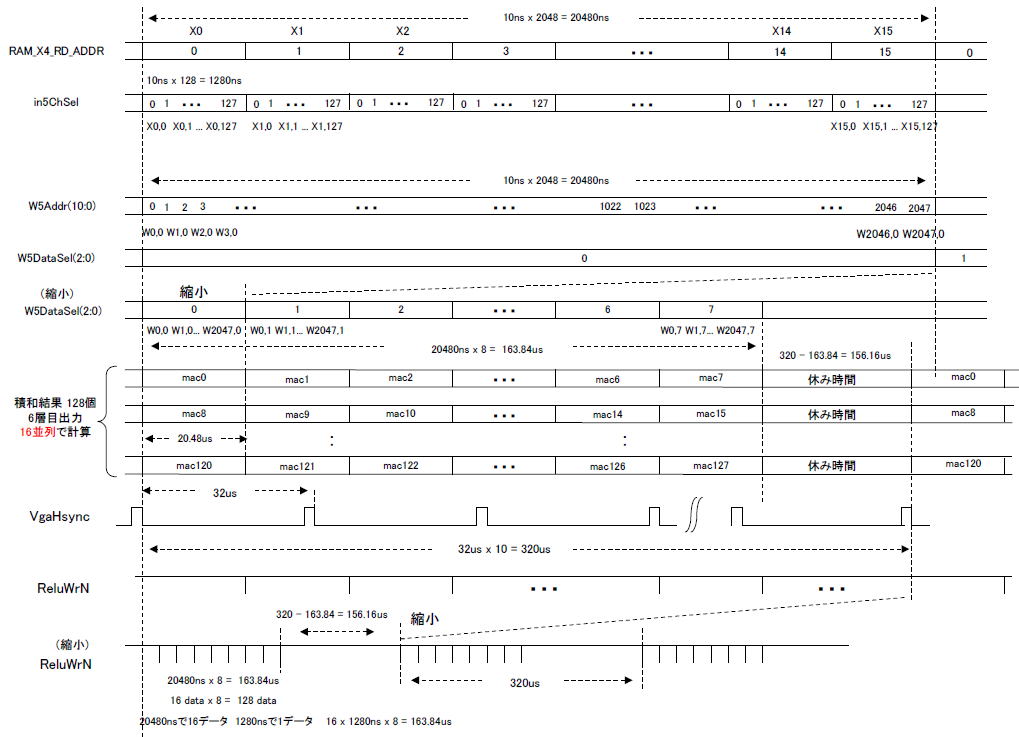

4層目はこのように1画面を320us(休み時間込み)で出力します。5層目も同様に320usで演算する必要があるため、乗算器16個で並列動作させます(理由はここ)。

図10‐21のRAM_X4_RD_ADDRは図10‐20のフレームバッファのアドレスで、まずアドレス0からデータX0を読みます。

その期間にin5ChSelという信号でデータX0をデマルチプレクスします。全640ビットから順に5ビットづつ、X0,0

X0,1 X0,2... X0,127と取り出して積和演算器に送り、重み係数とともに128回の積和が行われます。

次にアドレス1からデータX1が読まれ、X1,0 X1,1 X1,2... X1,127が取り出されて128回の積和が行われます。

同様にX2、X3... 最後にX15からそれぞれ128個が取り出され、合計128 x 16 = 2048回の積和が行われます。

その下のW5Addr(10:0)は重み係数のアドレスで、このROMのアドレス0〜2047まで、左端の列W0,0 W1,0 W2,0... W2047,0 が読み出されます。それらが上記の2048個のデータと積和され、最初の積和結果mac0になります。

その下の(縮小)ではW5DataSel(2:0)が0から1になり、そこではROMの隣の列W0,1 W1,1, W2,1... W2047,1が読み出されます。それらが上記の2048個のデータと積和され、それが次の積和結果mac1になります。

同様にW5DataSel(2:0)が0〜7まで繰り返され、積和結果mac0〜7までが得られます。 |