10乚01丂慡寢崌5憌栚偼擖椡2048夋慺丄弌椡128夋慺

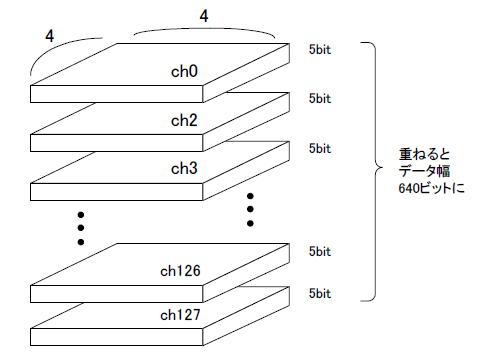

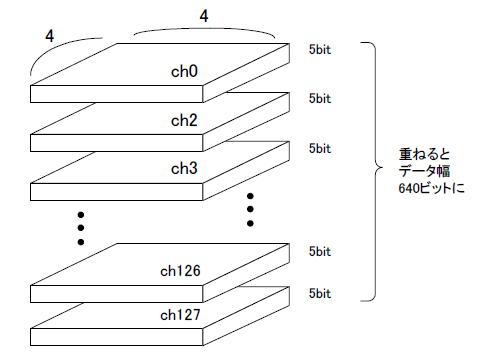

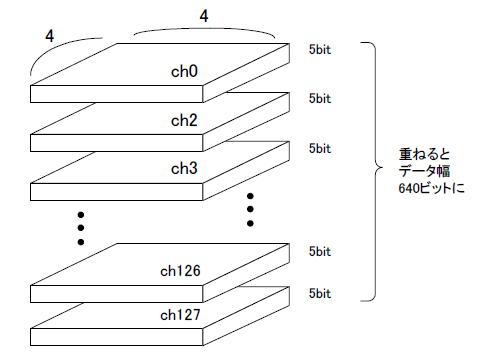

仠128僠儍僱儖偺夋柺傪廳偹傞僀儊乕僕

丂忯傒崬傒4憌栚偺弌椡偼128ch偁傝丄偦傟偧傟4亊4夋慺偁傝傑偡丅傑偨奺抣偼0乣31偵惂尷偝傟偰偍傝丄晞崋側偟5價僢僩偵側傝傑偡丅

丂4憌栚偺弌椡RAM偼恾10乚01偺傛偆偵128ch偺夋柺傪廳偹傞僀儊乕僕偱偡丅4x4側偺偱傾僪儗僗偼0乣15丄僨乕僞偺價僢僩暆偼640偵側傝丄偙傟偑5憌栚偺擖椡偵側傝傑偡乮仏侾乯丅

乮仏侾乯忯傒崬傒憌偱偼儔僀儞僶僢僼傽傪夘偟偰僨乕僞傪傗傝庢傝偟偨偑丄慡寢崌憌偱偼撉傒弌偟曽偑曄傢偭偰偔傞偺偱4憌栚偼僼儗乕儉僶僢僼傽偵彂偒崬傓丅

丂4憌栚偲5憌栚偺娫偵恾10乚01偺傛偆側僼儗乕儉僶僢僼傽傪2屄愝偗丄僺儞億儞儌乕僪偱僨乕僞傪傗傝庢傝偟傑偡丅偦偆偡傟偽乽彂偒側偑傜撉傓乿偙偲偑偱偒傑偡丅丂 |

恾10-01丂4憌栚偺弌椡丄5憌栚偺擖椡偑擖傞RAM

仠僨乕僞傪堦屄偯偮撉傫偱暘棧偟偰暲傋傞

丂恾10乚01偺僼儗乕儉儊儌儕偺傾僪儗僗0傪撉傓偲丄640價僢僩偺僨乕僞偑1屄摼傜傟傑偡丅偦傟傪5價僢僩偯偯暘棧偟偰墶偵128屄暲傋傑偡丅

丂師偵傾僪儗僗1傪撉傫偱墶偵128屄暲傋丄摨條偵傾僪儗僗2, 3, 4... 15傑偱撉傫偱暲傋丄偙偺傛偆偵寁128亊16亖2048屄墶堦峴偵暲傋傑偡丅偙傟偑5憌栚偺擖椡偵側傝傑偡丅

仠5憌栚偐傜偼Dense乮慡寢崌宆乯偵側傞

丂5憌栚偺廳傒峴楍偼2048峴亊128楍偱丄偙偺傛偆偵擖椡偲忔嶼偟傑偡丅忔嶼寢壥偼128夋慺偵側傝丄偦傟偵僶僀傾僗傪壛嶼偟偨傕偺偑6憌栚偺擖椡偲側傝傑偡丅慡寢崌憌偱偼偙偺傛偆側扨弮側峴楍忔嶼仌僶僀傾僗壛嶼傪峴偄傑偡丅 |

仠5憌栚偼16暲楍偱寁嶼

丂5憌栚偺峴楍忔嶼偼2048 x 128夞偺忔嶼偑昁梫偵側傝丄忔嶼婍堦屄偱峴偆偲262,144僒僀僋儖丄偡側傢偪僋儘僢僋100MHz偱2621.44us偐偐傝傑偡丅CNN偺1僽儘僢僋偼320us枅偵擖偭偰偔傞偺偱偙傟偱偼娫偵崌偄傑偣傫丅

丂偦偙偱忔嶼婍傪16屄巊偭偰暲楍偵張棟偟傑偡丅2621.44us/16 = 163.84us偵側傝丄娫偵崌偆偙偲偑暘偐傝傑偡丅

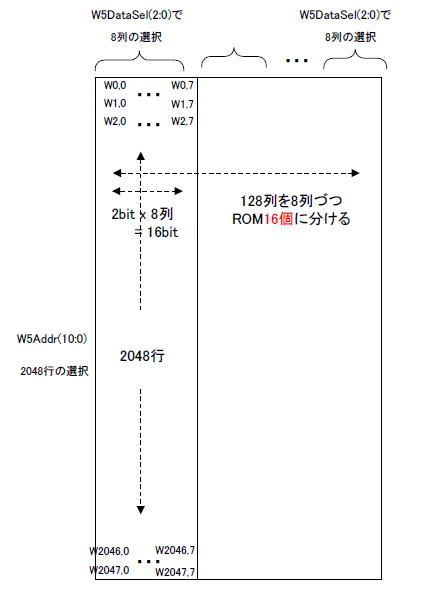

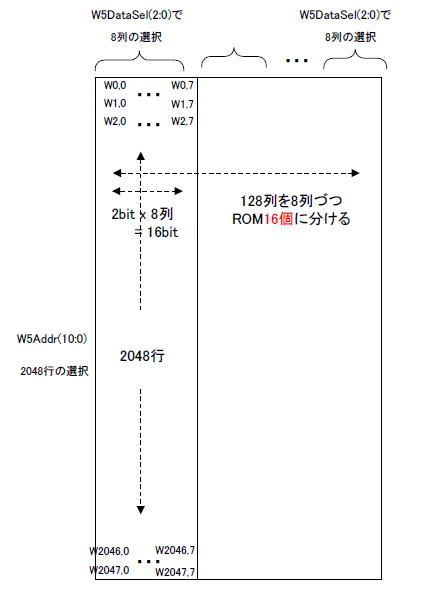

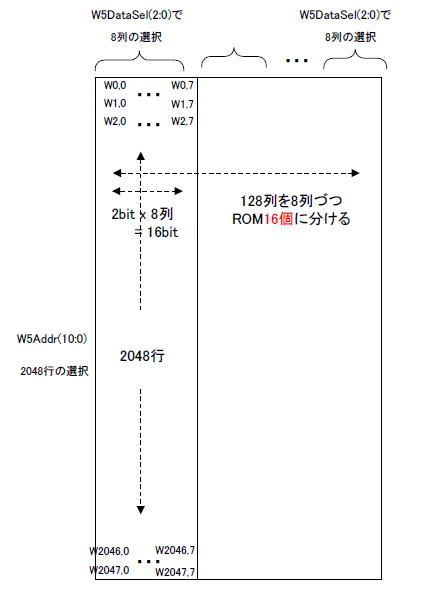

仠ROM傕16暲楍偱撉傒弌偡

丂廳傒學悢傪1偮偺ROM偵抲偄偰偟傑偆偲丄堦搙偵學悢1屄偟偐撉傒弌偣傑偣傫乮億乕僩偑1偮側偺偱乯丅偟偨偑偭偰恾10乚02偺傛偆偵ROM傪16屄偵暘偗丄僨乕僞傪16屄摨帪偵撉傒弌偣傞傛偆偵偟傑偡丅 |

恾10乚02丂128楍傪8楍偛偲16屄偵暘偗傞

仠廳傒學悢偑堦斣懡偄5憌栚

丂偙傟傜16屄偺ROM偺偆偪1屄偺ROM偵拲栚偡傞偲丄偦傟偼2048峴亊8楍偁傝傑偡丅偟偨偑偭偰偱傾僪儗僗偼11價僢僩丄偦偟偰奺傾僪儗僗偵8屄偺學悢偑懚嵼偡傞偙偲偵側傝傑偡丅

丂傑偨5憌栚偺廳傒學悢偼4庬椶偵尷掕偝傟偰偄傞偺偱學悢1屄偼2價僢僩偱昞尰偱偒傑偡丅偟偨偑偭偰傾僪儗僗11價僢僩丄僨乕僞暆 2x8= 16價僢僩偺ROM偑16屄偁傞偙偲偵側傝傑偡丅

丂5憌栚傕忔嶼偼價僢僩僔僼僩宆偱峴偄傑偡丅學悢偺悢偼2048 x 128 = 262,144偲慡憌偺拞偱嵟傕懡偔側傝傑偡丅偙傟傜學悢ROM傕VBA傪偮偐偭偰HDL壔偟傑偡丅 |

師偺儁乕僕傊

栚師傊栠傞

|