7-02 層間の画像メモリは4行ぶんあればよい!?

●層間のデータの受け渡しにはメモリが必要

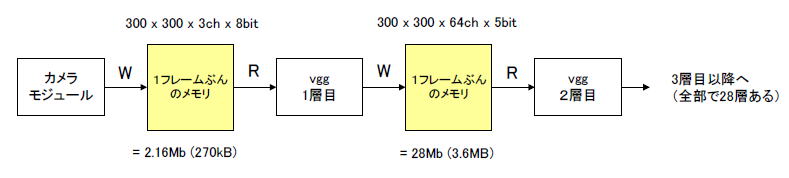

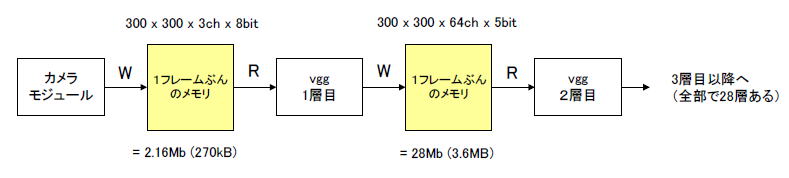

SSD物体認識の入力画素数は300×300あります(ここの左上)。1層目の入力は3ch、画素は8ビットなので、図7‐06では300 x 300 x

3ch x 8bit = 2.16Mb (270kB)のメモリを使ってカメラからのデータを受け取っています。

また2層目は入力が64ch、画素は5ビットです。従って同図では300 x 300 x 64ch x 5bit = 28Mb (3.6MB)のメモリで1層目からのデータを受け取っています。 |

図7-06 フレームメモリがチャネル数ぶん・・・メモリ不足になる

●カーネルサイズが3×3・・・ということは・・・

例えばこのFPGA(Cyclone V 5CGTD9)には13.917Mb (1.74MB)のEmbedded Memoryがあります。FPGA内部メモリとしてはかなり大きいほうですが、図7‐06のような使い方をすると2層目で早くもメモリ容量が尽きてしまいます。

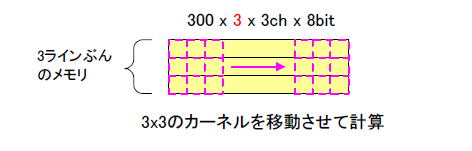

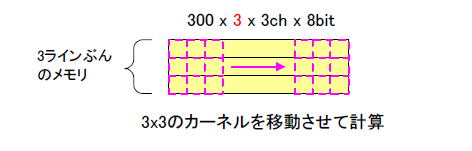

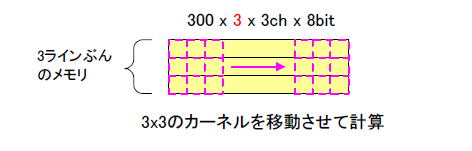

ここで、本企画のSSDのカーネルサイズは3×3だったことを思い出しましょう。それを図7‐07のように横にずらしながら畳み込みを行います。さしあたりは3行ぶんのメモリがあれば十分ということに気が付きます。 |

図7-07 3行ぶんあればどうにかなりそう

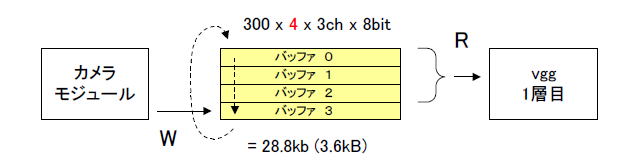

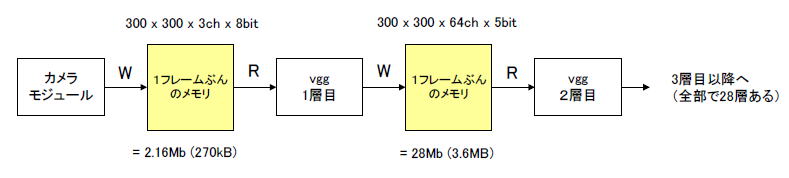

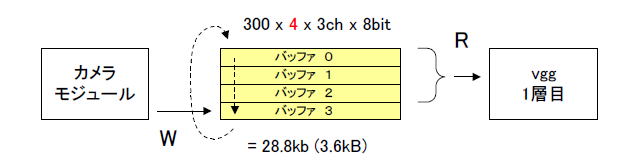

●3+1で4ラインぶんあればよい

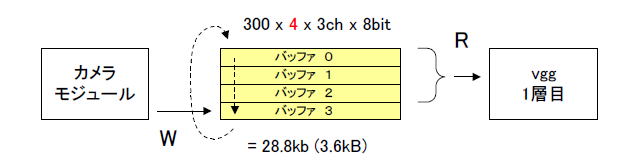

本企画は「リアルタイム画像処理」を目指すので、「書きながら読む」工夫が必要になります。従って実際は図7‐08のように1ライン増やして4ラインぶんの画像メモリを設けます。1層目は同図のように300

x 4 x 3ch x 8bit = 28.8kb (3.6kB)で済みます。 |

図7‐08 書き方(W)を追いかける読み方(R)

●書いていないバッファを読めば安全に読める

1ラインぶん余分に設けることにより「書きながら読む」ことができます。例えばバッファ3を書いているとき、はバッファ0,1,2を読みます。図7‐09のように書き方(W)を追いかけるように、読み方(R)は書いていない3ラインを読みます。 |

図7‐09 1ライン書く間、書いていない3ラインを読む

次のページへ

目次へ戻る |