8-07 vgg-14, 15層目のVHDL化(続き)

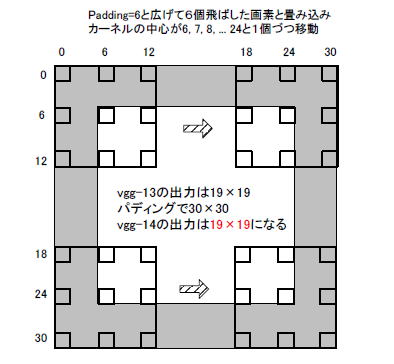

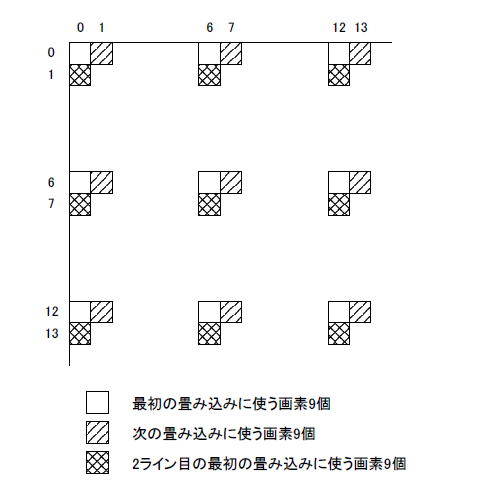

図8-124 画像を広げて間を空けて畳み込み

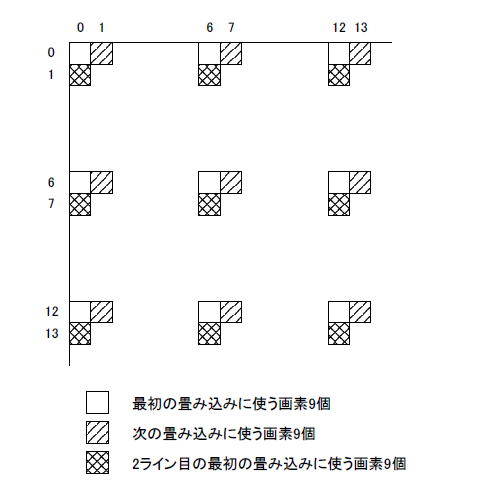

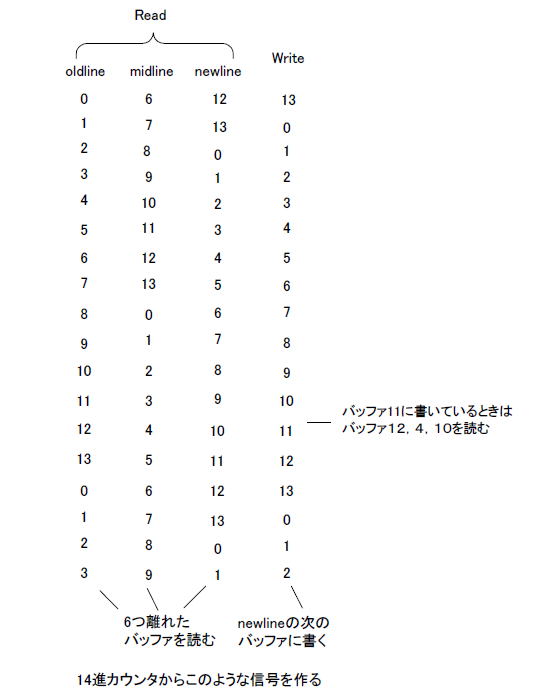

図8-125 画素間が開くのでその分メモリが必要

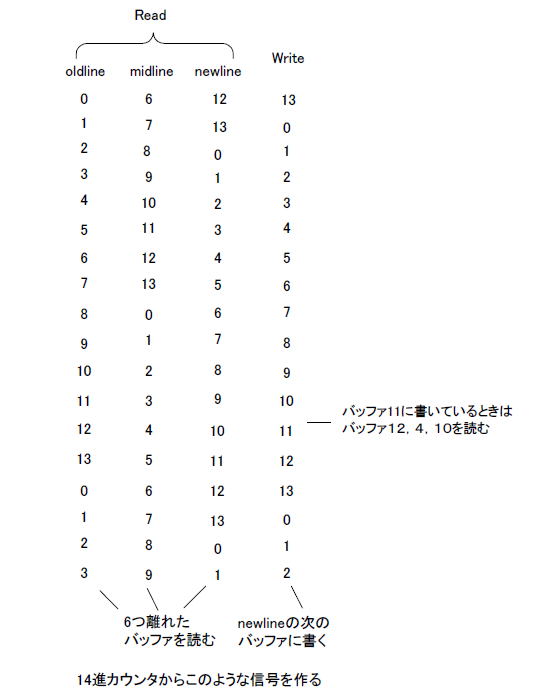

図8-126 書き方(Write)と読み方(newline, midline, oldline)の関係

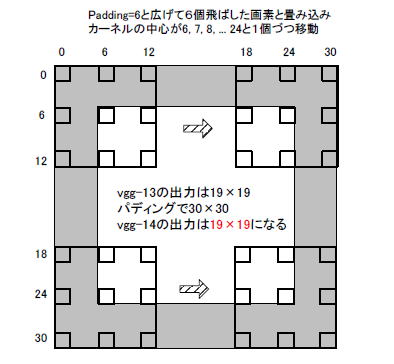

図8‐127 書き方(Write)を追いかける読み方(oldline, midline, newline) 次のページへ 目次へ戻る |

||||||||||||||||

8-07 vgg-14, 15層目のVHDL化(続き)

図8-124 画像を広げて間を空けて畳み込み

図8-125 画素間が開くのでその分メモリが必要

図8-126 書き方(Write)と読み方(newline, midline, oldline)の関係

図8‐127 書き方(Write)を追いかける読み方(oldline, midline, newline) 次のページへ 目次へ戻る |

||||||||||||||||