8-07 vgg-14, 15層目のVHDL化(続き)

●ラインバッファの読み出し選択を見る

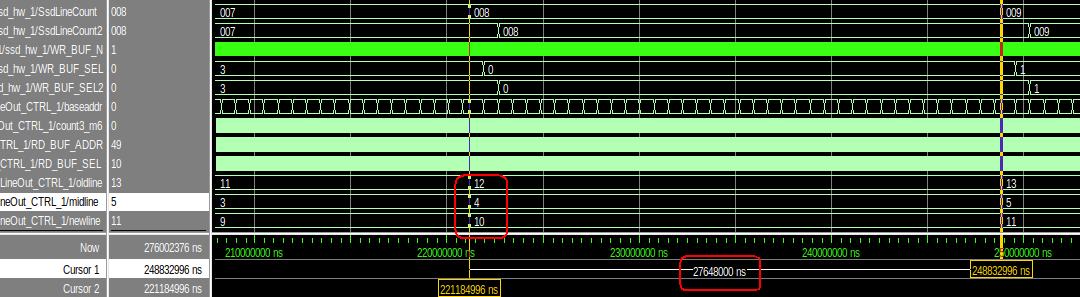

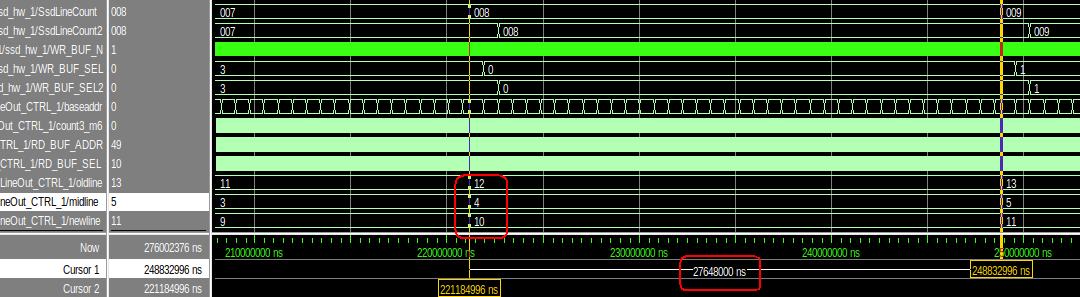

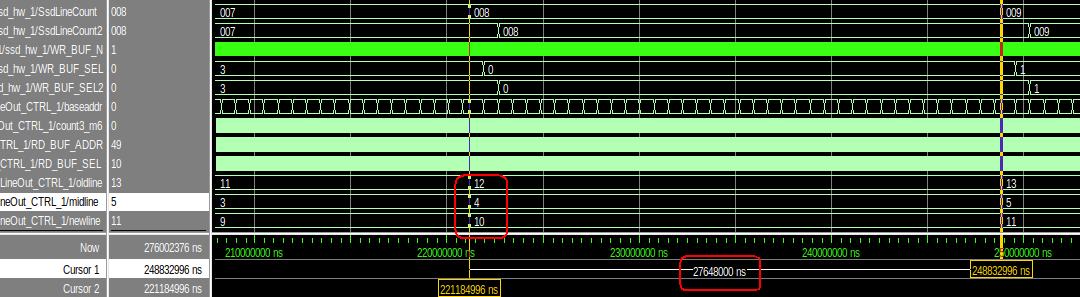

図8‐129は論理シミュレーションのラインバッファ読み出し選択の部分です。oddline,

midline, newlineそれぞれ12,4,10になっています。このコンビネーションが27.648ms続きます(1ラインの周期)。 |

図8-129 バッファを選択する3つの信号

●左端の画素の畳み込みを見る

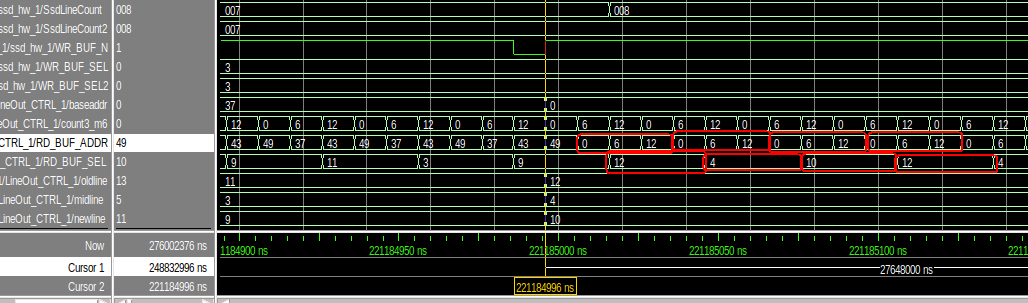

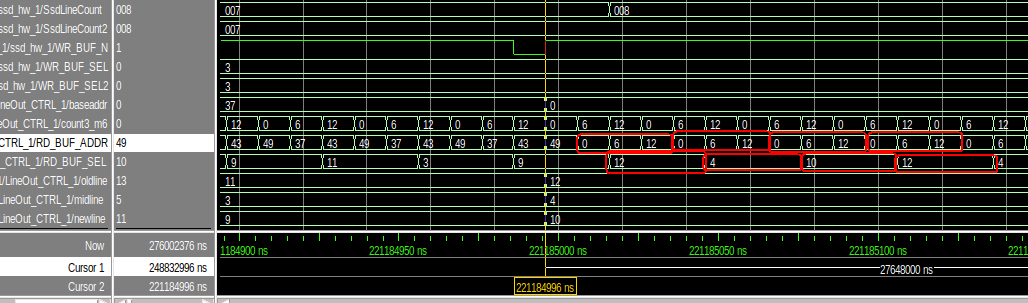

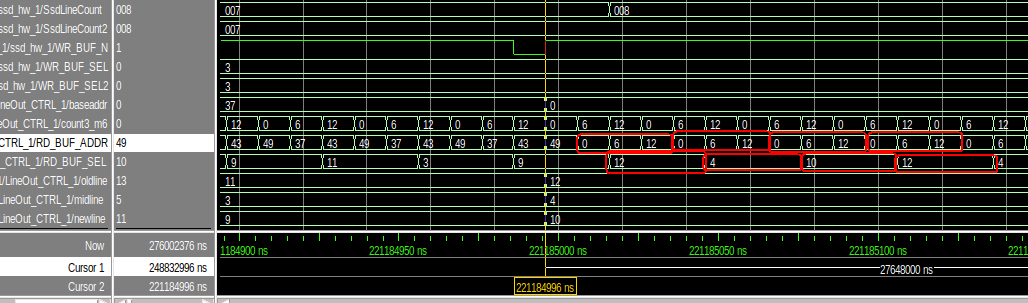

図8‐130のRD_BUF_ADDRはラインバッファの読出しアドレス、RD_BUF_SELはラインバッファの選択信号です(意図的に1サイクル遅らせてある)。0,

6, 12と横方向に6つおきのアドレス、12, 4, 10と縦方向に6つおきのバッファ選択になっています。 |

図8-130 画素の選択とバッファの選択

●右端の画像の畳み込みは

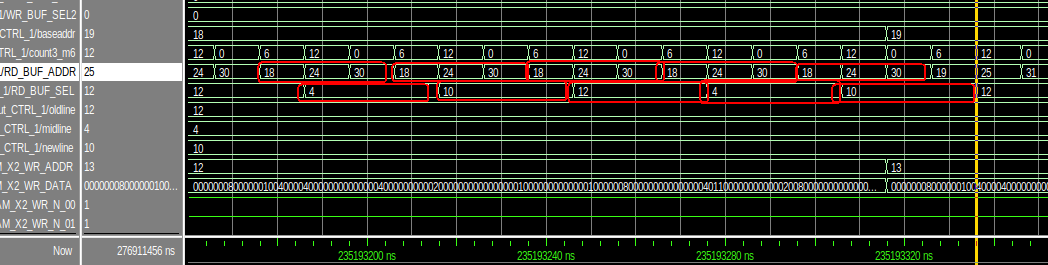

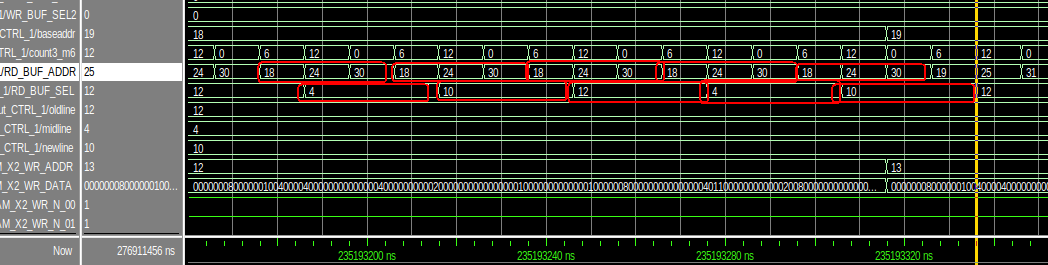

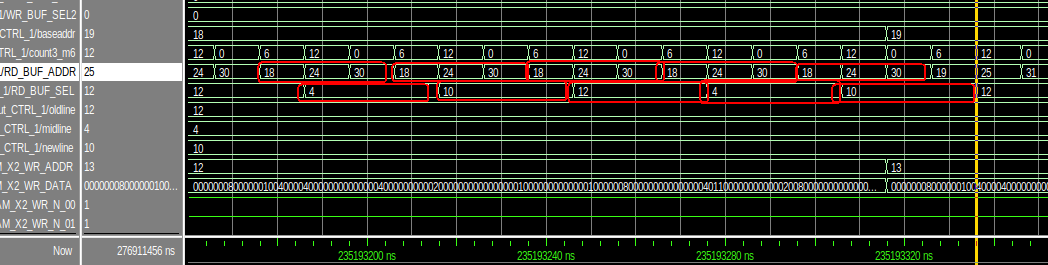

図8‐131は1ライン畳み込みの最後の画素の部分、18, 24, 30と横方向に6つおきのアドレス(padding = 6 のおかげで最後の画素アドレスは30になる)、12, 4, 10と縦方向に6つおきのバッファ選択になっています。 |

図8-131 19x19がパディングで31x31となったので最後は18, 24, 30

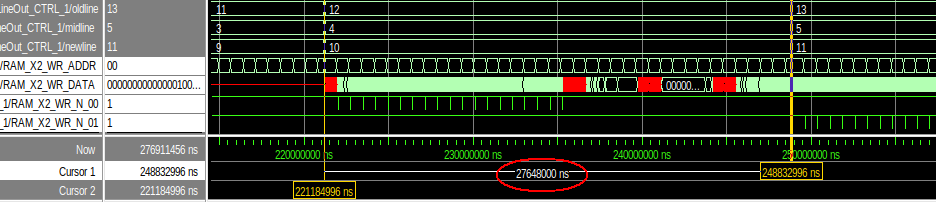

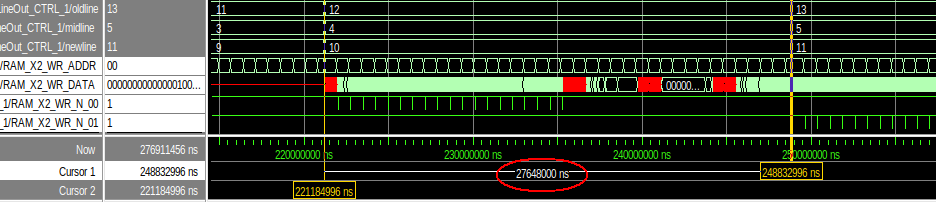

●畳み込み以外はほぼ前層と一緒(出力は1024chに増える)

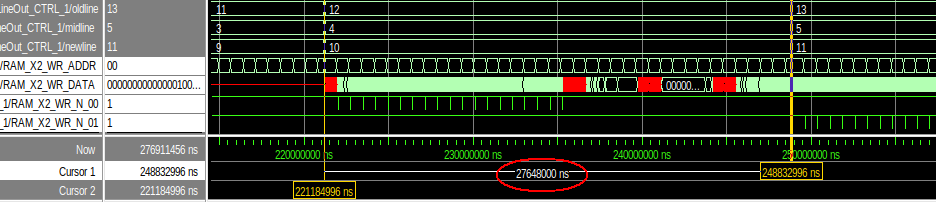

パディングやダイレーションの違いはあるものの画素数は19x19のままなので1ラインの計算周期は前層と同じ27.648msになります。また次層はカーネルが1x1なので出力用のバッファは2個あれば十分です(RAM_X2_00,

01)。 |

図8‐132 1ラインに27.648ms、1画面の計算はその19倍になる

●relu.outに出力が書かれている

14層目も出力はテキストファイルに落とされます。19×19画素なので1画面で361行、また出力は1024チャネルなのでビット幅は

5bit x 1024 = 5120bit になります。これをVBAで1024個のCSVファイルに分割してPythonの結果と比較します。 |

●バッチファイルでまとめて比較する

CSVファイルが1024個もあるので、前層までと同様にバッチファイルによって比較し、全てのチャネルがピタリ一致することを確認します。 |

次のページへ

目次へ戻る |