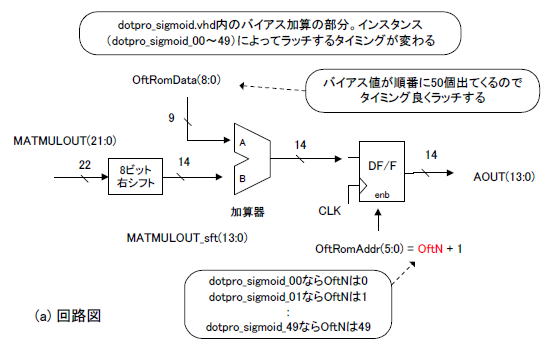

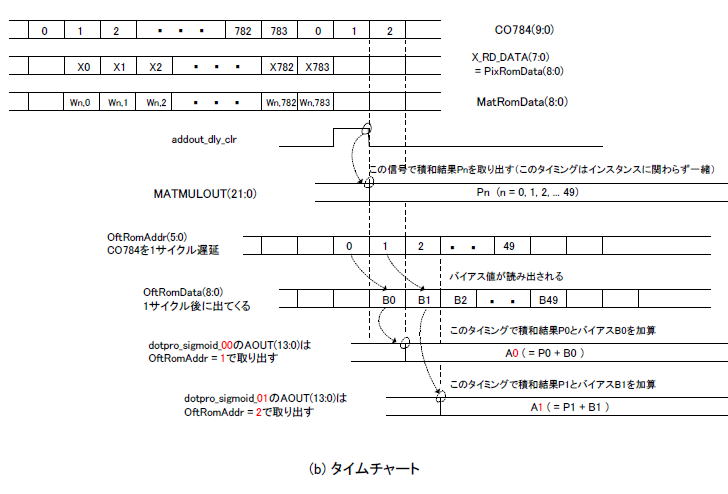

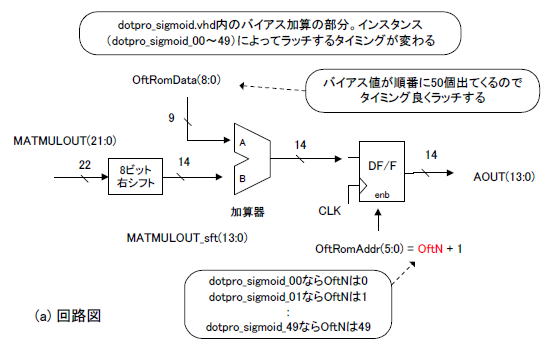

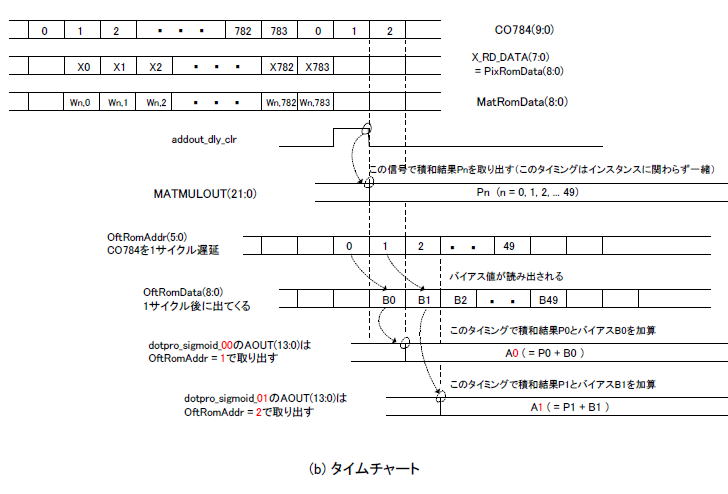

図3-03(b)のようにMATMULOUTは、addout_dly_clr(CO784=1)のタイミングでラッチされ、CO784=2の時刻で有効になります。

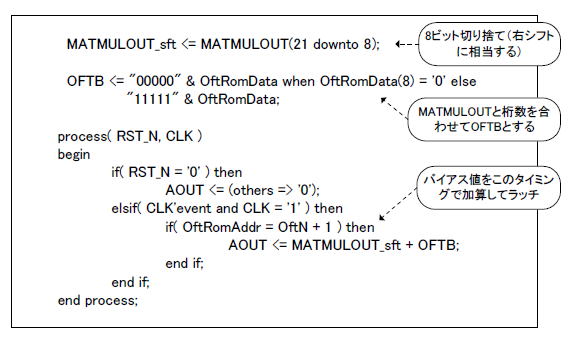

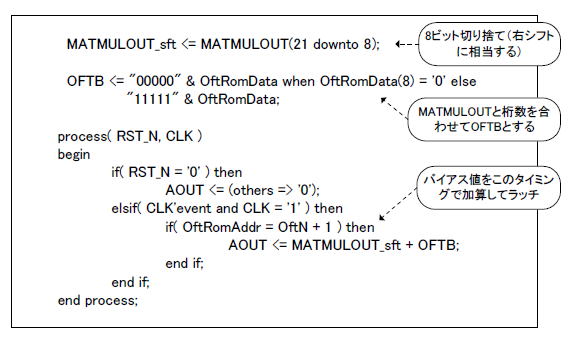

またOftRomDataも同時刻から有効になります。OftRomAddrはCO784を1サイクル遅延したものなので、同図のようにOftRomAddr=1のときに加算器の出力をラッチすれば正しい演算結果が得られます(*2)。

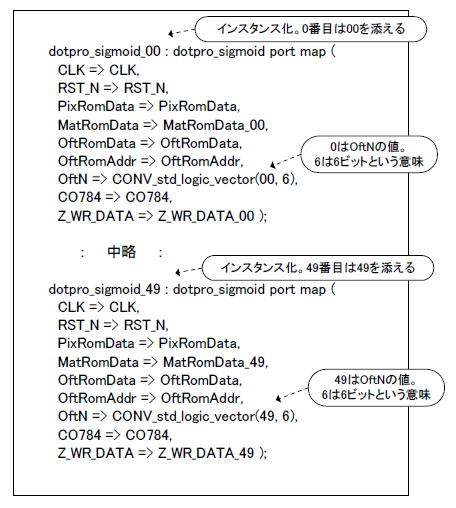

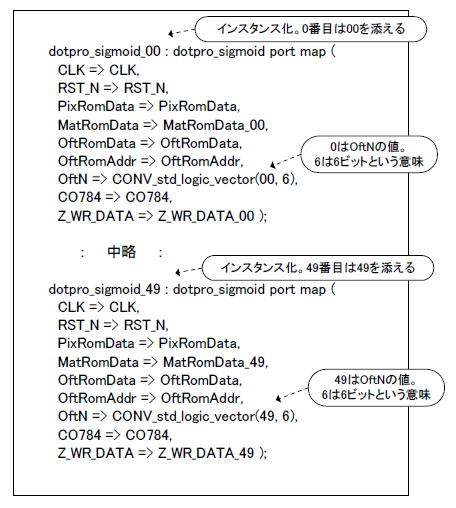

(*2)1層目の行列は784x50なので、各列の積和結果は50個、バイアスも50個ある。したがって各インスタンスdotpro_sigmoid_00〜49の番号とバイアスOftRomData_00〜49のタイミングを合わせる必要がある。

バイアスを加算した信号AOUTはシグモイド関数に入力されます。その回路は図2-07と同じです。シグモイドの出力はZ_WR_DATAとなり、1層目の結果RAM (RAM_Z1)に書き込まれます。 |