4-02 カメラエミュレータROMのHDL生成(続き)

●テスト画像をFPGAで処理する

カメラエミュレータはシミュレーションだけではなくFPGA実機でも使用します。

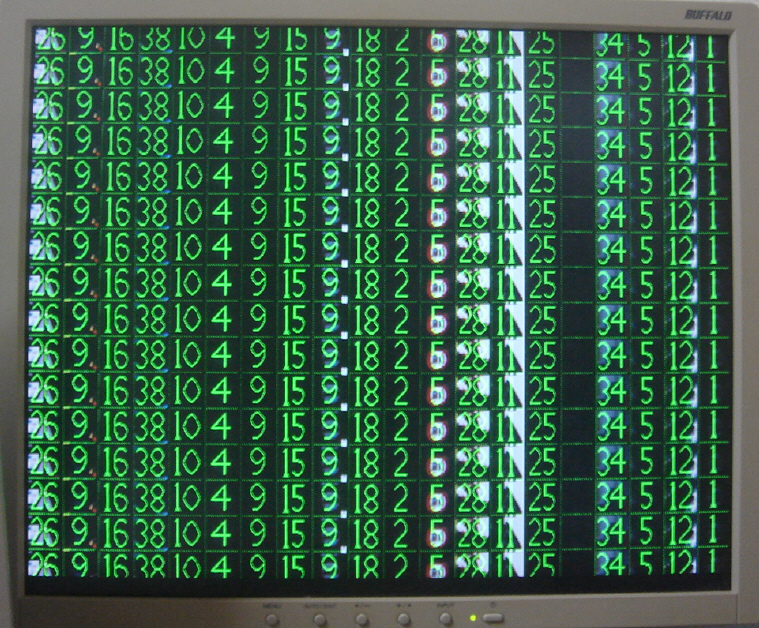

エミュレーションモード(図4‐03でEMUMODE=1)とすると、先ほど生成したROM_CAM_00〜29.vhdが選択され、VGAモニタは図4‐11のようになります。これは図4‐02の20枚の画像が横一行に並んだもので、それが縦に16行繰り返されます。 |

図4‐11 カメラ動画の代わりにGTSRBテスト画像がVGAに

●VGA 640×480 のエリアいっぱいに20枚の画像

画像はそれぞれ30×30ですが、このように2画素ぶん「隙間」があるので、横一ラインは32×20 = 640、RGB565(計16ビット)を8ビットづづに分離していることを鑑みて×2=1280個のデータになります。

ROM_CAM_00.vhdには横一ラインぶんのデータが1280個あり、アドレス数はキリの良い2048になります。

HDLファイルはROM_CAM_00〜29の30個(30ラインぶん、画像の縦方向が30画素なので)あります。縦方向には隙間がなく、この30ラインが繰り返し16回表示されて

30 x 16 = 480が縦一ラインの画素数になります。

図4‐11は画像をスルーでVGAに映していますが、推論結果を上書きすると図4‐12のようになります。 |

図4‐12 各推論クラス割り当てられた数字を表示

●テスト画像20枚の推論結果

推論結果が緑色で書かれています(背景にうっすらと元画像が見える)。左端は26なので、これを見ると(26.png) 正解していることが分かります。

その隣は9, 16, 38... と正解していますが、右の方に一つ数字が抜けています。これは6層目(最終層)の出力が閾値を超えなかったため、判定できなかったということです。

●FPGA内部でPython/Excelと同じことが起こることを確認

また実機でカメラエミュレータを使用すると、FPGA内部信号(図4-13)とPython/Excelとの一致を見ることもできます。 |

図4‐13 ロジックアナライザでFPGA内部信号を見る

最初のページへ

目次へ戻る

|