8‐03 3層目のRAMアクセス(読み方/書き方)

●3層目の入力RAMの読み方

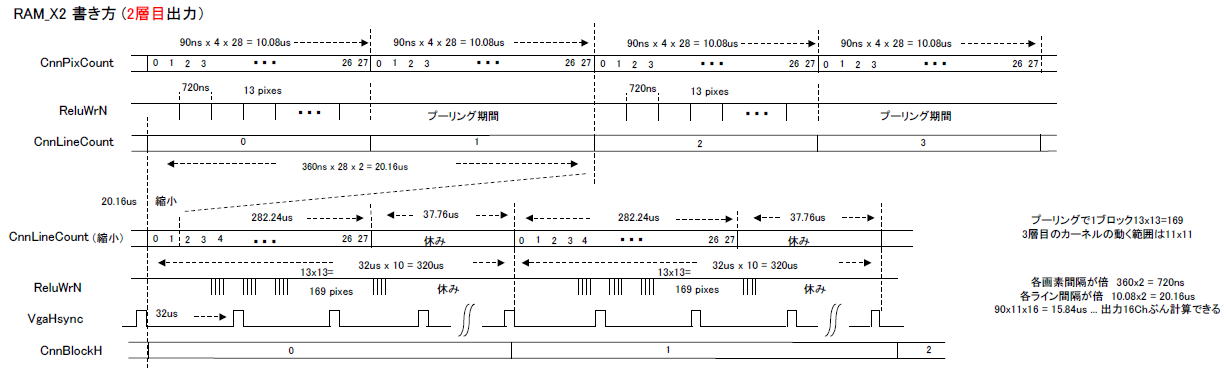

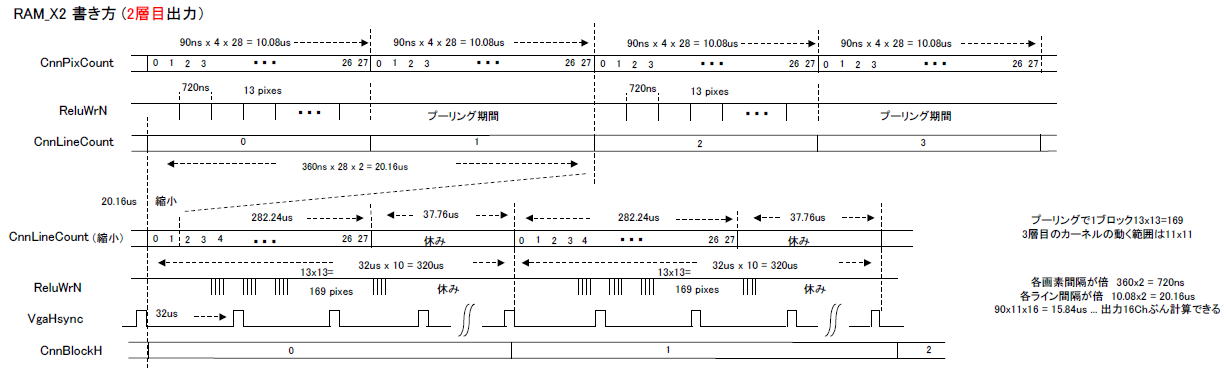

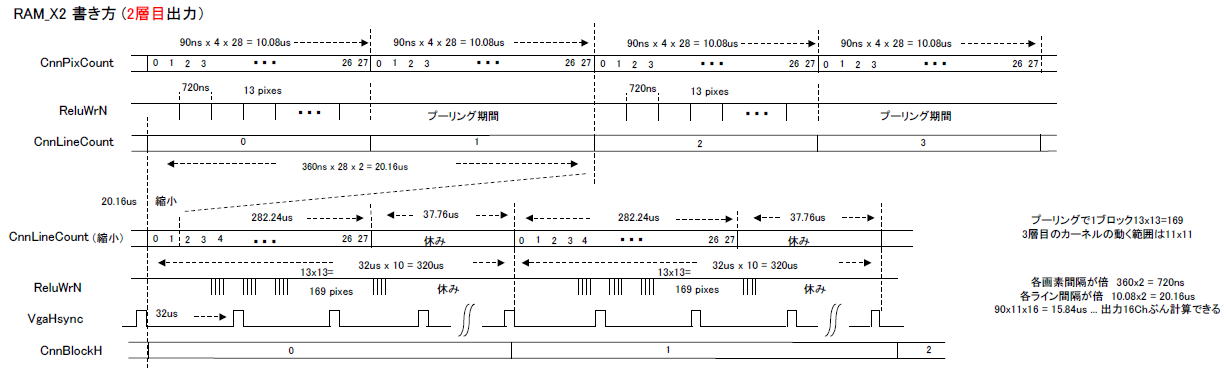

2層目と3層目のデータのやり取りはラインバッファRAM_X2を使って行われます。2層目は図8‐20の上の方、1画素出力に720ns、1ライン13画素出力するのに20.16usになります。

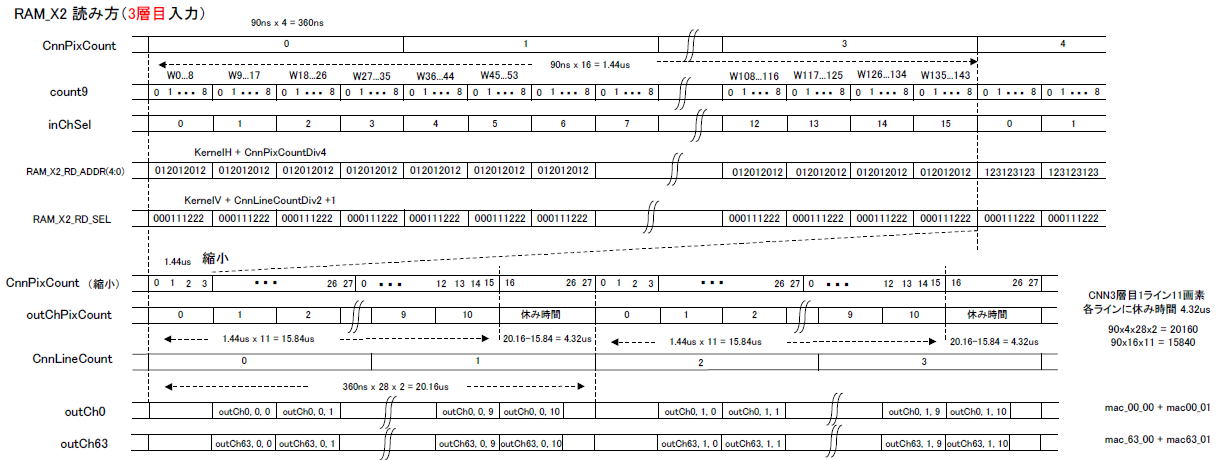

したがって3層目も20.16usで1ライン11画素演算する必要があります。図8‐21の下の方、outCh0, 0, 0〜outCh0,

0, 10(出力Ch0の横一行11画素)は20.16us以内に計算されています。出力はCh63まで64並列なので、全チャネルが20.16us以内に計算されます。 |

図8-20 RAM_X2書き方

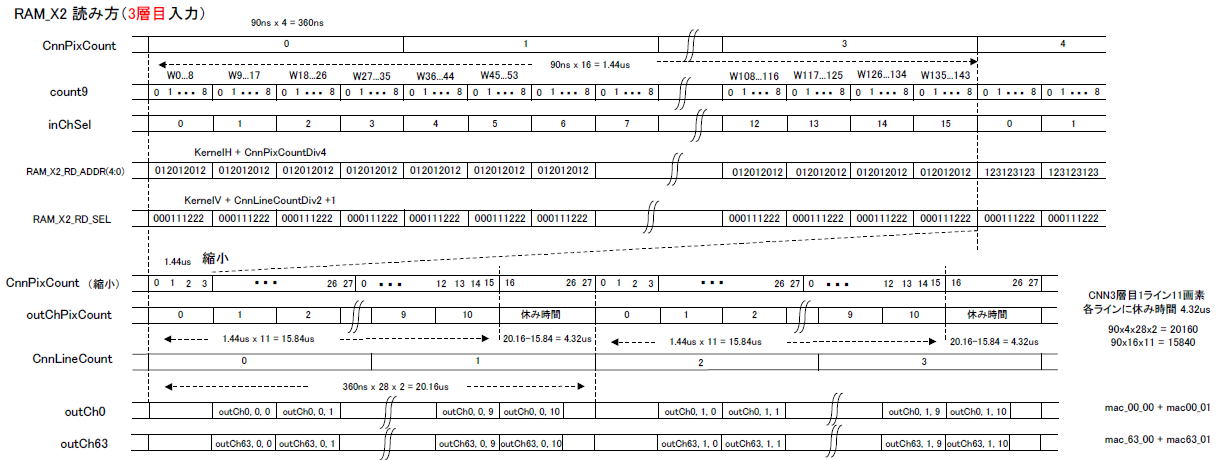

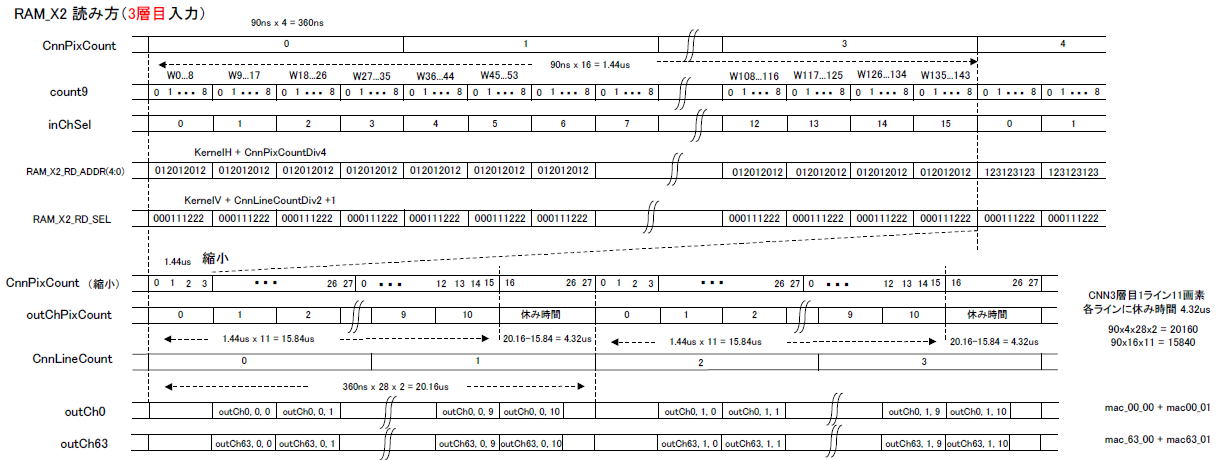

図8-21 RAM_X2読み方

●入力16chを逐次計算しても間に合う

3層目はこのように入力16Chを一つの積和演算器が受け持ちます。各Ch毎にカーネル3x3があるので図8‐21の上の方、count9を16回、90ns

x 16 = 1.44usで係数や画素を読み出します。その下のinChSelは16個の入力Chを選択する信号です。

RAM_X2_RD_ADDRはラインバッファのアドレス、RAM_X2_RD_SELはラインバッファの選択信号で、図8‐21のように生成すれば、このようなバッファアクセスができます。

1.44us毎に出力1画素を計算するので横1ライン計算するのに 1.44us x 11 =

15.84usになりますが、2層目が1ライン出力する時間20.16usなので、それに合わせて待ち時間を加えてパイプライン動作させます。 |

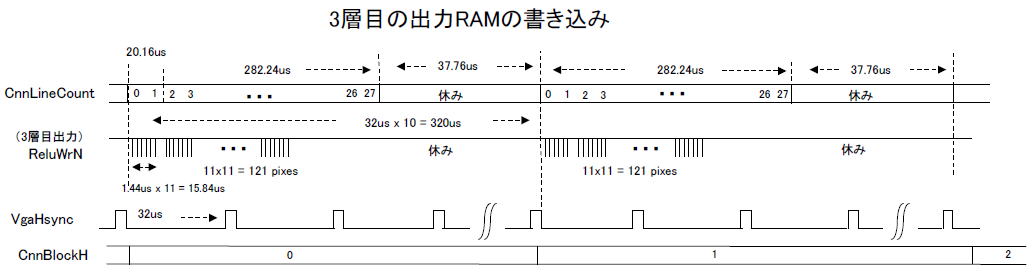

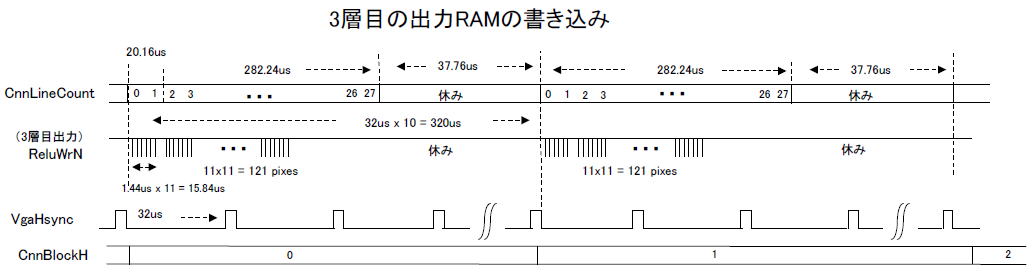

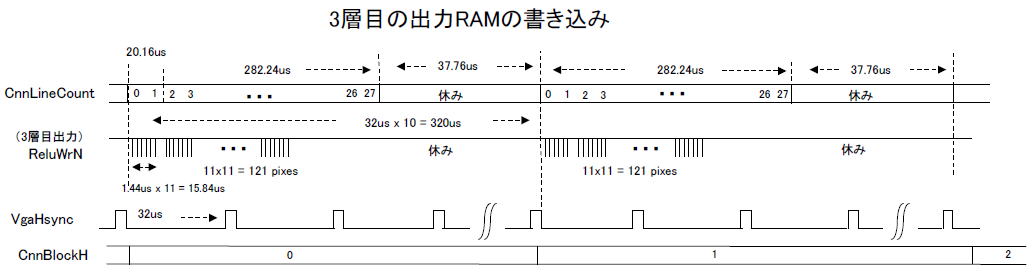

●3層目の出力RAMの書き方

図8‐22は3層目の書き込みのタイミングで、1.44usの間隔で1画素、1.44us x 11 = 15.84us+休み時間で20.16usの間隔で画素が11個(1ラインぶん)書き込まれます。

さらにそれを11ラインぶん繰り返して1画面ぶん書き込まれますが、その時間は20.16us

x 11 = 221.76us+休み時間で 320usになります。

このように各層ライン単位、画面単位で同期をとりながら計算させます。 |

図8‐22 RAM_X3の書き込み(3層目出力)

次のページへ

目次へ戻る

|