9乚05丂4憌栚僔儈儏儗乕僔儑儞偲EXCEL偺摎偊崌傢偣

仠4憌栚偼弌椡偑128ch偵側傞

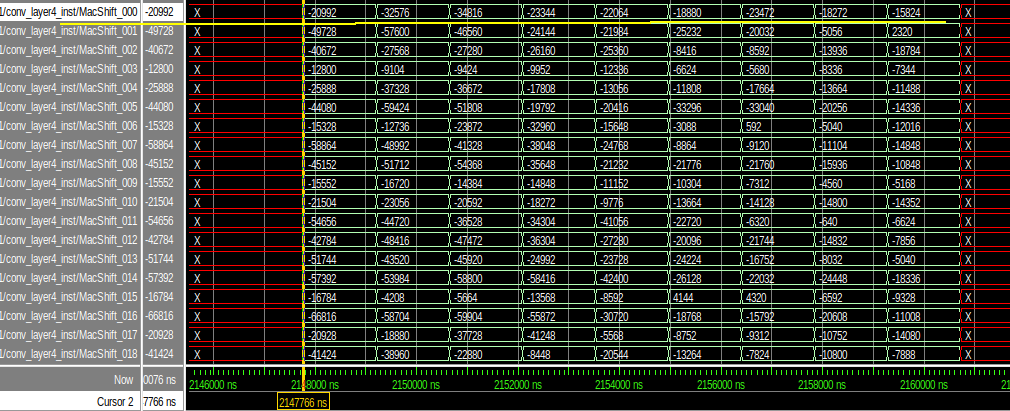

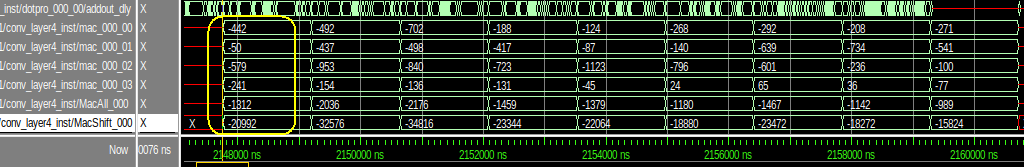

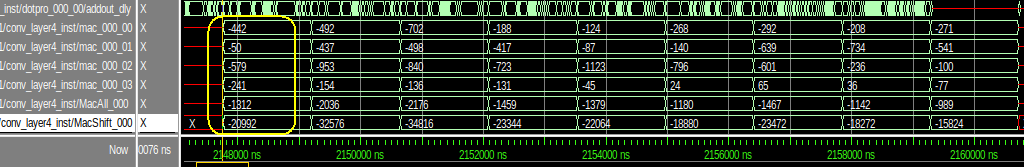

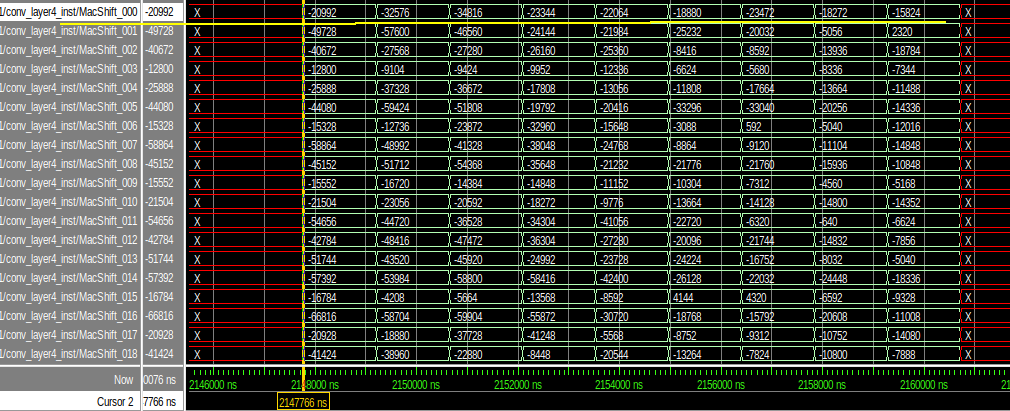

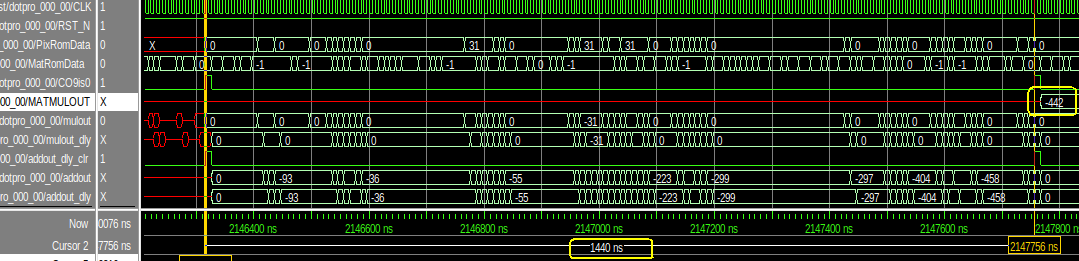

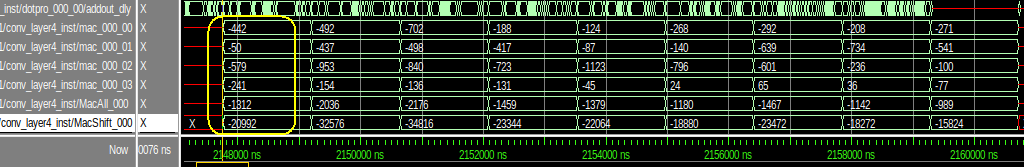

丂恾9乚50偼僔儈儏儗乕僔儑儞傪2.147ms傎偳憱傜偣偨曈傝丄tb_VideoProc/VideoProcCore/gts_hw/conv_layer4/MacShift_00乣127偲偄偭偨怣崋傪尒偰偄傑偡丅 |

恾9-50丂128ch偺寢壥偑摨帪偵弌偰偔傞

仠愊榓墘嶼偑崌偭偰偄傞偐偼EXCEL偲斾妑

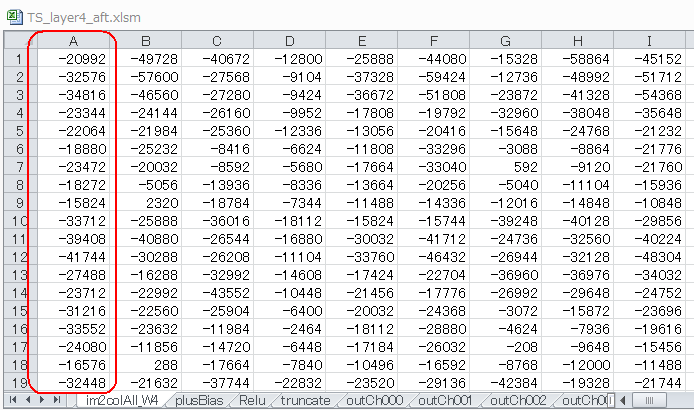

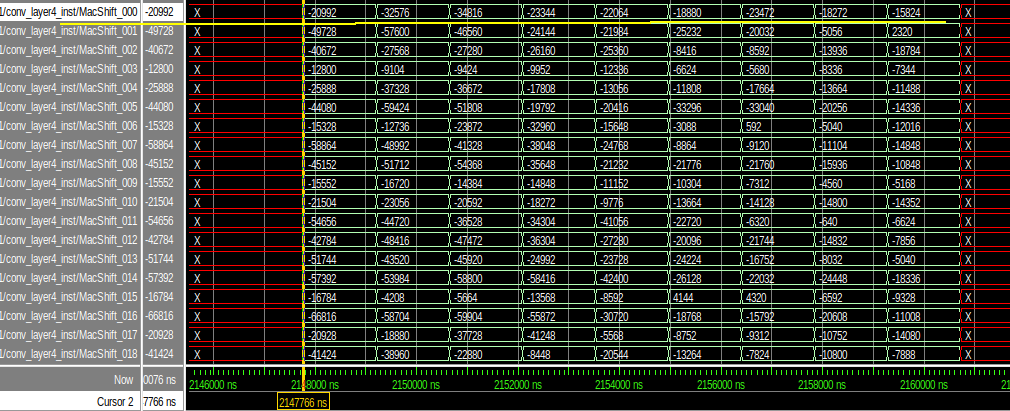

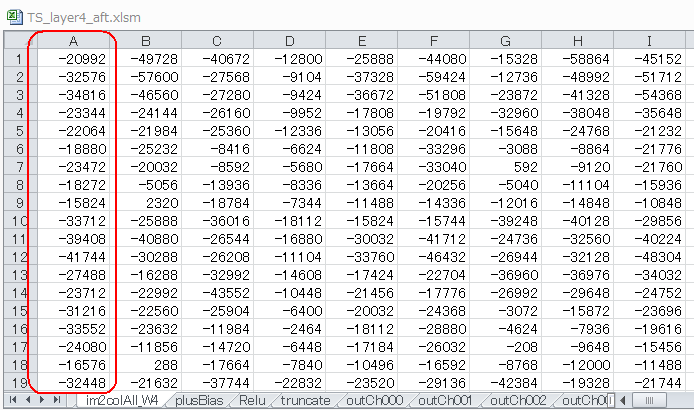

丂恾9乚51偼4憌栚偺EXCEL僼傽僀儖(TS_layer4.xlsm)偺im2colAll_W4僔乕僩偱偡丅偙傟偼峴楍忔嶼偺64枃偺僔乕僩im2col00_W4乣im2col63_W4傪懌偟崬傫偩傕偺偱偡乮擖椡偑64ch側偺偱64枃懌偟崬傫偱1枃乯丅

丂摨恾偺A楍傪尒傞偲恾9乚50偺MacShift_00偺抣偲僺僞儕堦抳偟偰偄傞偙偲偑暘偐傝傑偡丅椬偺B楍偼MacShift_01丄偦偺椬C楍偼MacShift_02...

塃抂偺DX楍偑MacShift_127偲摍偟偄偙偲傪妋擣偟傑偟傚偆乮弌椡偑128ch側偺偱128楍偁傞乯丅 |

恾9-51丂im2colAll_W4僔乕僩偲斾妑

仠堦偮偺愊榓墘嶼婍偺堦偮偺墘嶼寢壥偵拲栚

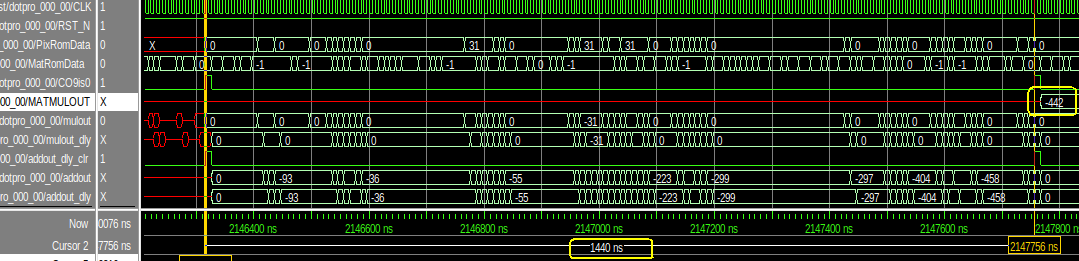

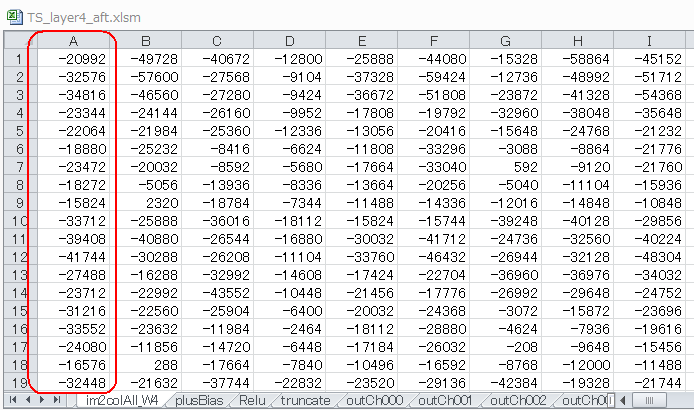

丂恾9乚51偺嵍忋偺-20992偵拲栚偟丄偦偺抣傪媮傔傞夁掱傪尒偰傒傑偡丅恾9乚52偼conv_layer4/dotpro_000_00乮愊榓墘嶼婍乯偺怣崋偱偡丅

丂摨恾偺嵍偺榞撪PixRomData乮夋憸僨乕僞乯偑31丄MatRomData乮廳傒學悢乯偑-1丄mulout乮忔嶼寢壥乯偑-31偵側偭偰偄傑偡丅

丂塃偺榞撪偼PixRomData偑6丄MatRomData偑1丄mulout偑24偵側偭偰偄傑偡丅 |

恾9乚52丂學悢偼2價僢僩丅11側傜-1攞丄01側傜4攞

仠學悢偺庬椶偼係偮偵廤栺偝傟偰偄傞

丂4憌栚偺學悢偼2價僢僩偵僄儞僐乕僪偝傟偰偍傝丄傑偲傔傞偲師偺昞偺傛偆偵側傝傑偡丅乽杮棃忔嶼偝傟傞傋偒抣乿偺1/16偑忔嶼偝傟偰偄傑偡丅 |

| 學悢乮2恑乯 |

學悢乮10恑乯 |

忔嶼偝傟傞抣 |

杮棃忔嶼偝傟傞傋偒抣 |

| 01 |

1 |

4 |

64 |

| 00 |

0 |

1 |

16 |

| 11 |

-1 |

-1 |

-16 |

| 10 |

-2 |

-4 |

-64 |

丂丂昞9乚01丂忔嶼寢壥偼杮棃偺1/16偺抣偵側傞偙偲偵拲堄

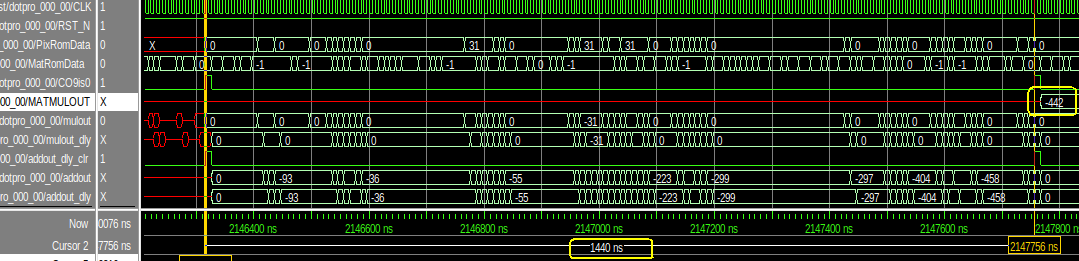

仠堦偮偺愊榓墘嶼婍偑擖椡16ch庴偗帩偮乮擖椡偼64ch偁傞乯

丂恾9乚53偱偼3亊3亊16ch亖144僒僀僋儖乮1440ns)偐偗偰愊榓偑峴傢傟丄MATMULOUT乮mac_000_00偲摨偠怣崋乯偺塃抂偵-442偑弌偰偄傑偡丅4憌栚偼偙偺恾偺傛偆偵愊榓墘嶼婍4偮偱弌椡1ch傪寁嶼偡傞偺偱丄偙偺mac_000_00偵傕偆嶰偮偺愊榓寢壥mac_000_01,

02, 03傪懌偟傑偡丅 |

恾9乚53丂僇乕僱儖偼3亊3丄擖椡16ch傇傫144夞偺愊榓傪偡傞

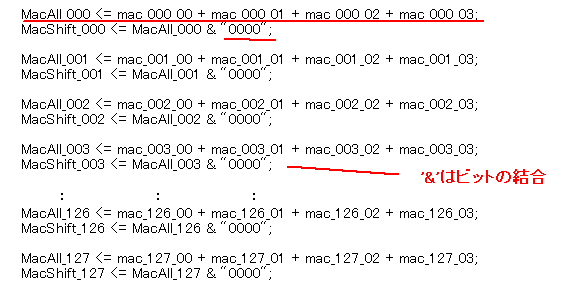

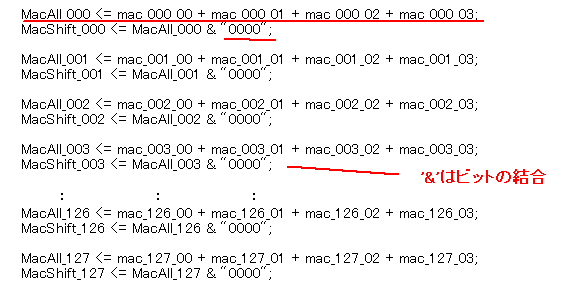

仠4價僢僩嵍僔僼僩偟偰16攞

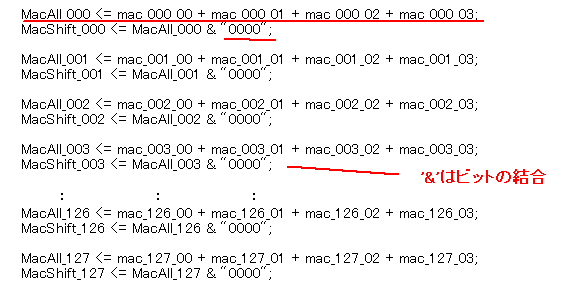

丂恾9乚54偺傛偆偵HDL偱偼mac_000_00, 01, 02傪壛嶼偟偰MacAll_000偲偟偰丄峏偵16攞偟偰MacShift_000偲偟傑偡丅奺愊榓墘嶼婍偱抣偑1/16側偭偰偄傞乮昞9乚01乯偺傪憡嶦偟傑偡丅 |

恾9乚54丂conv_layer4.vhd偺堦晹

仠弌椡Ch0偺寢壥傪EXCEL偲斾妑

丂恾9乚55偺榞撪丄-442-50-579-241 = -1312偲側傝丄偝傜偵16攞偱乚20992偲側傝丄EXCEL(恾9乚51乯偺嵍忋偺抣偲堦抳偟傑偡丅 |

恾9乚55丂僔儈儏儗乕僔儑儞偱弌椡ch0偺奺夋慺傪妋擣

師偺儁乕僕傊

栚師傊栠傞

|