9‐05 4層目シミュレーションとEXCELの答え合わせ(続き)

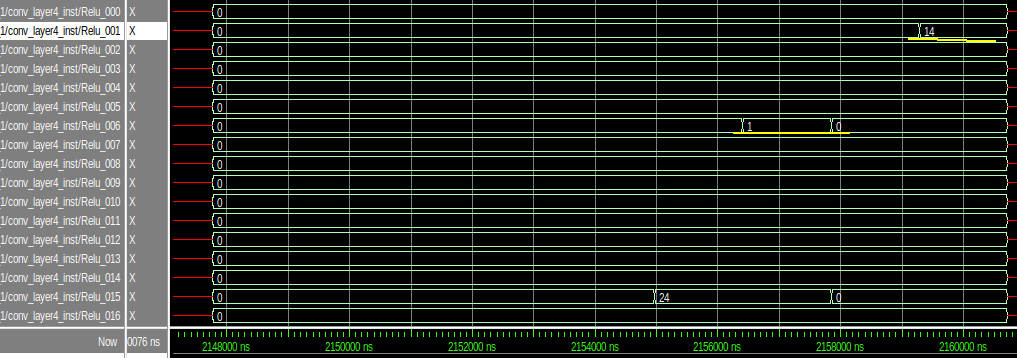

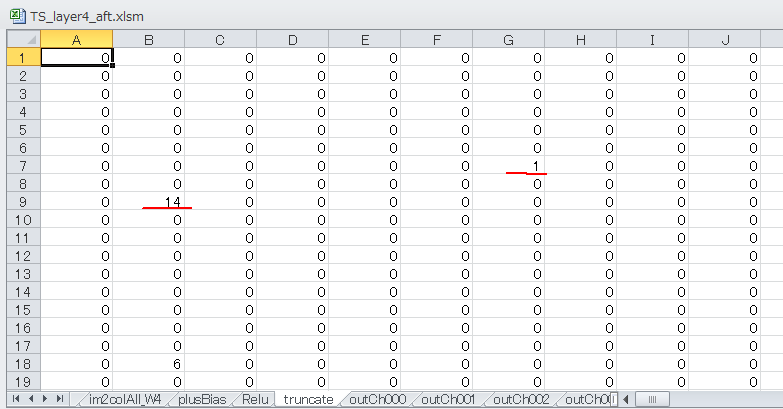

●EXCELのtruncateシートとRelu_xxを比較

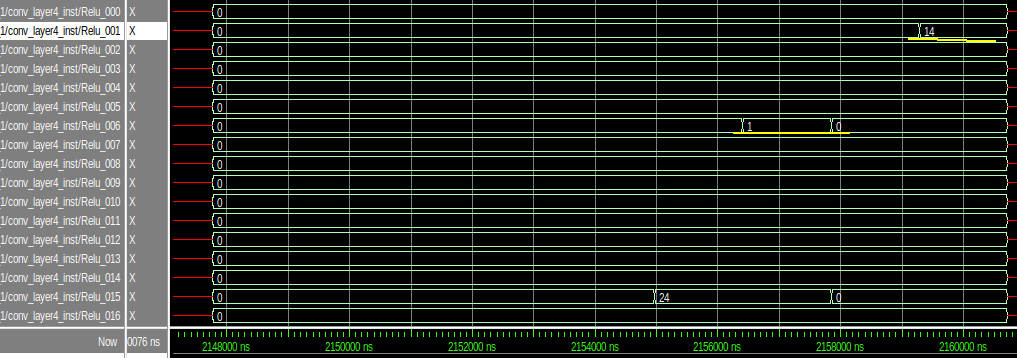

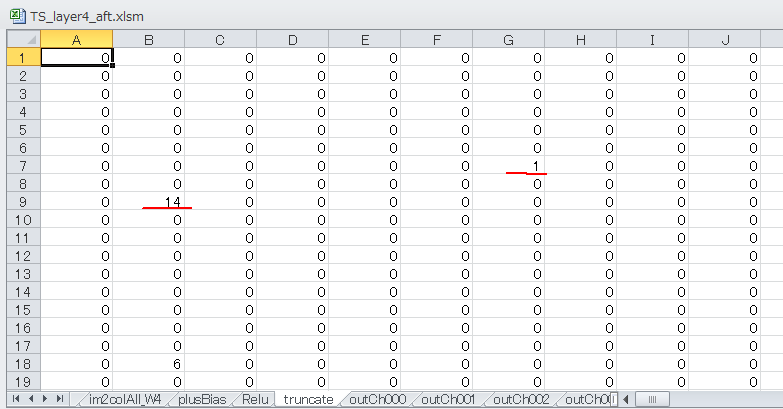

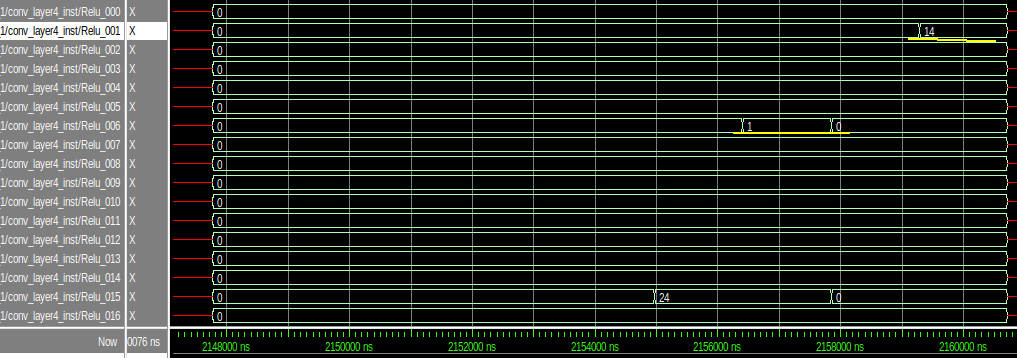

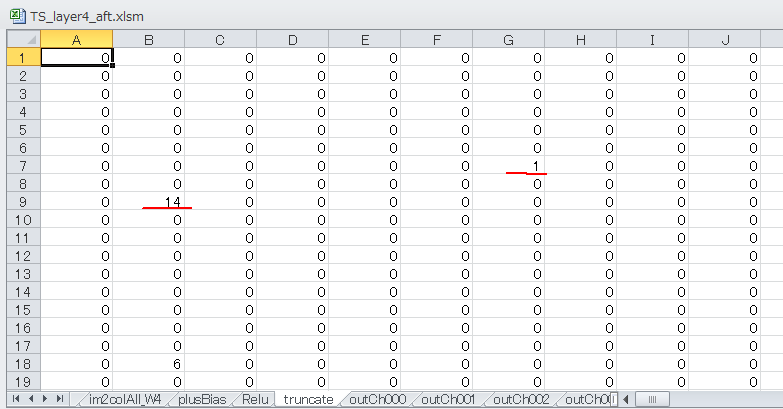

積和演算の後はバイアス加算、8ビットシフト、ReLUを経てRelu_00〜63となります(図9‐60(a))。同図(b)はEXCELのtruncateシートですが、Relu_00がA列、Relu_01がB列・・・Relu_127がDX列とピタリ一致することを確認します。 |

図9-60 (a) 4層目の出力(シム)

図9-60 (b) 4層目の出力(EXCEL)

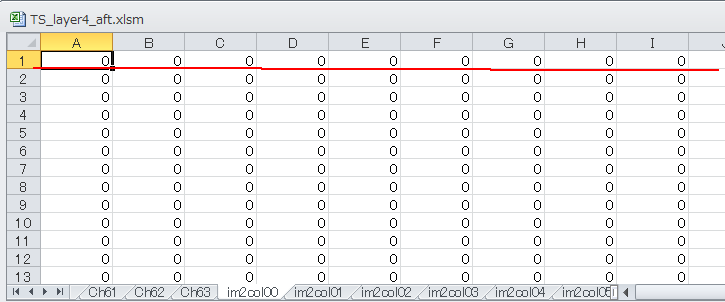

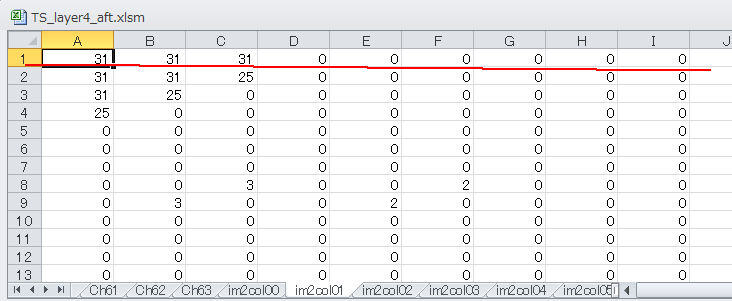

●積和結果が合わないとき−入力画素データはEXCELと合っているか

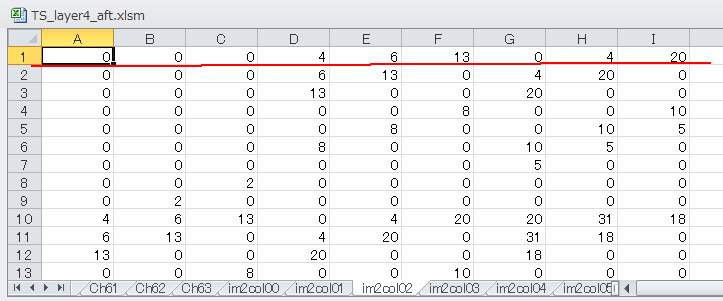

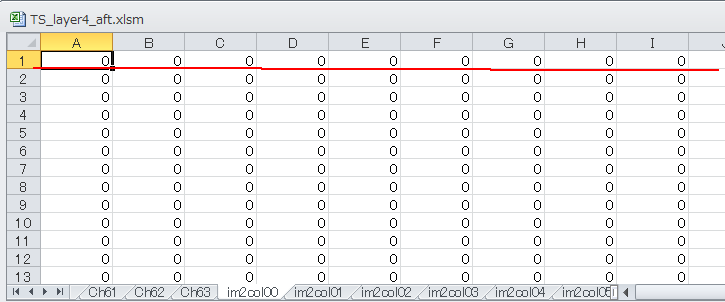

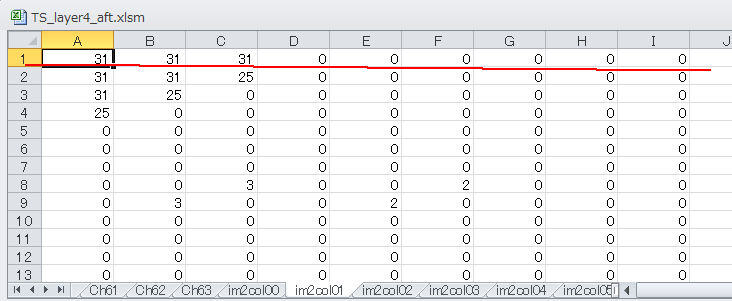

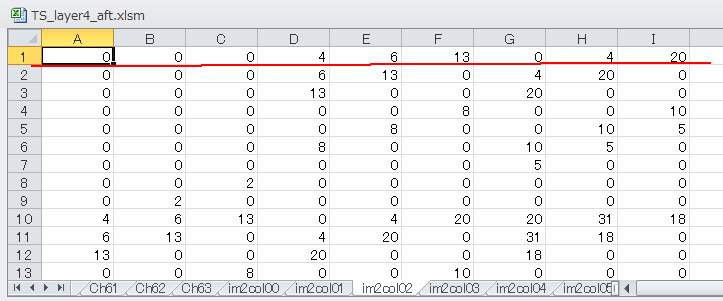

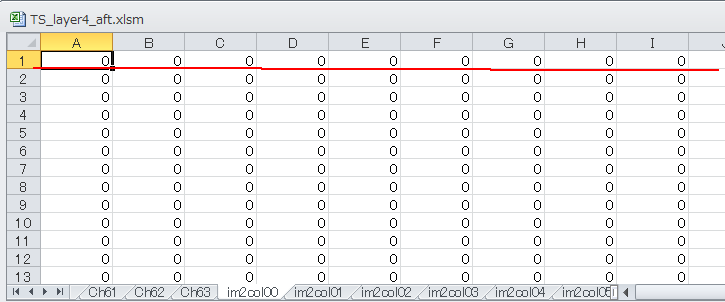

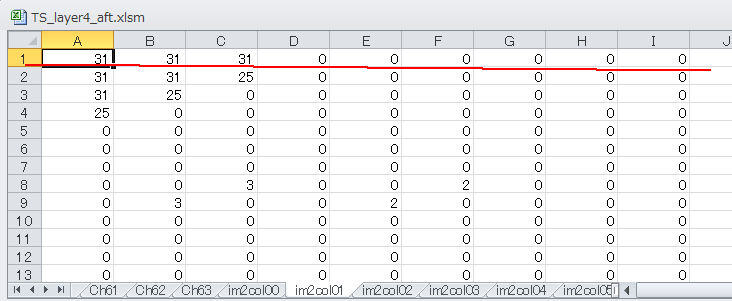

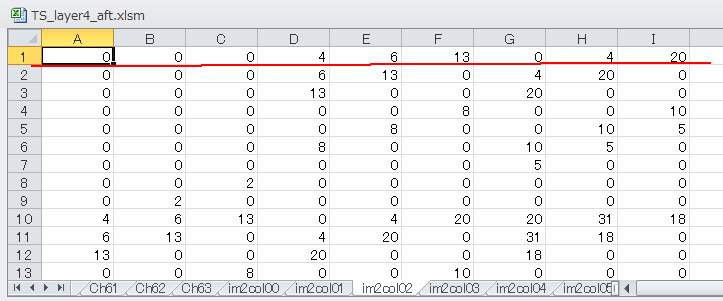

図9‐61はEXCELのim2col00, 01, 02シートで、これらは入力ch0, 1, 2の画素を9×9→9×81に並び替えたものです。

それぞれの一行目を並べたものが図9‐52のPixRomDataの値になっています。4層目はこの図のように一つの積和演算器が入力16chを受け持つので、PixRomDataはこの後、16chぶん続きます(im2col03〜15と比較)。 |

図9-61 im2col00, 01, 02。入力16ch(im2col00〜15)が1セットになる。

●重み係数はEXCELと合っているか

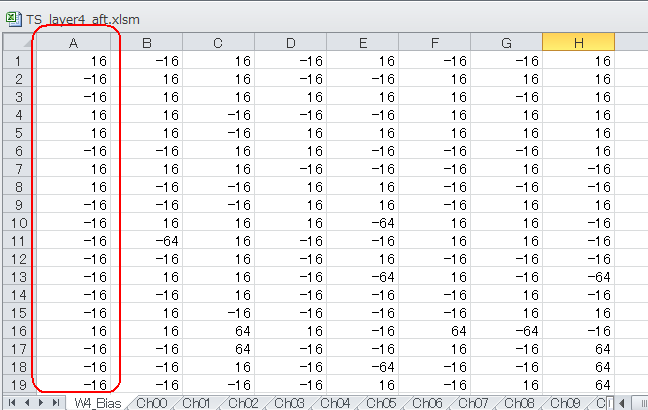

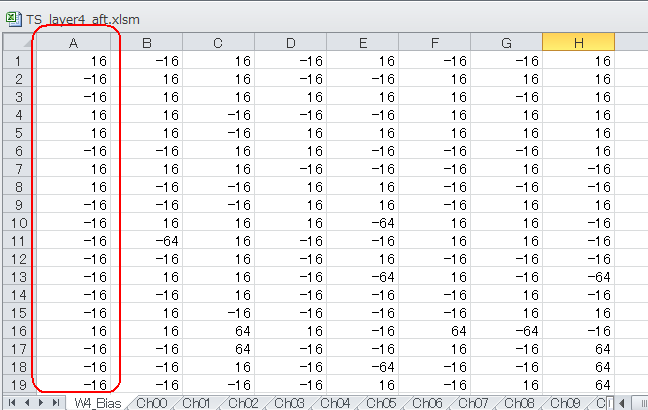

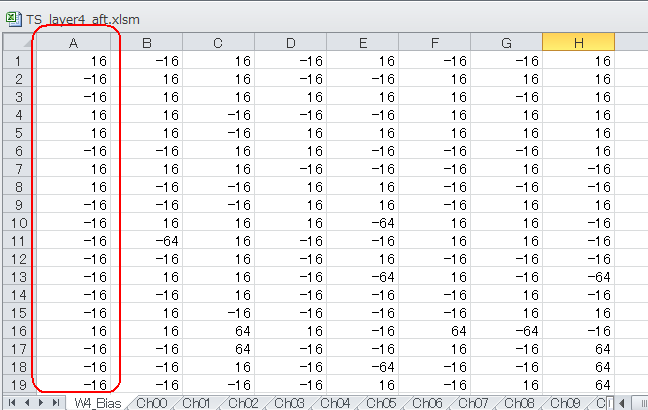

図9‐62はW4_Biasシートで、A列の16ch×9個の係数が図9‐52のMatRomDataとなっています(この表のようにエンコードされる)。 |

図9-62 重み係数9×16chぶん、A列144個で1セット

●4×4画素を320usで書いて5層目へ

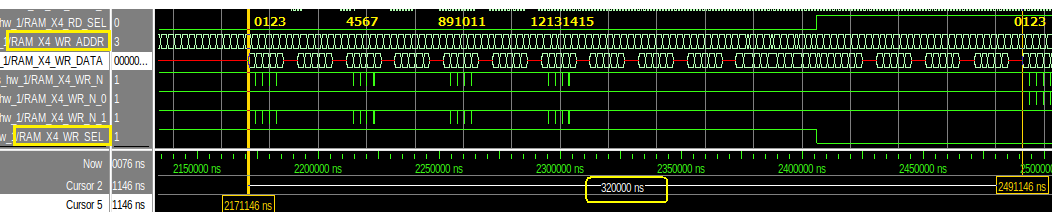

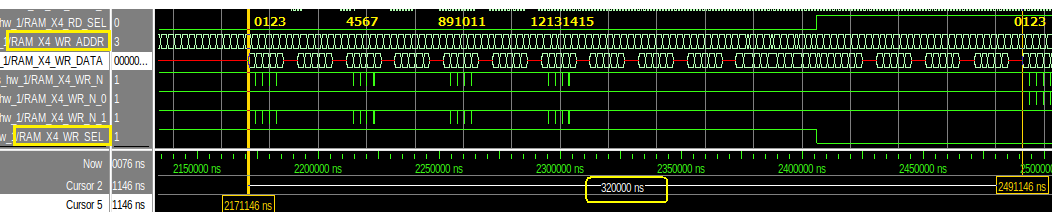

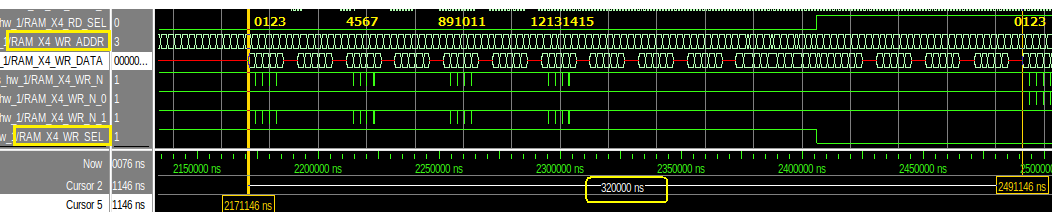

4層目はプーリングがあるので画素数が9×9→4×4と間引かれます(ここ参照)。

図9‐63は4層目の出力RAMの信号です。CNN1ブロックを処理する時間は320us、その時間内にRAM_X4_WR_N_Xが4ラインぶんLになっています。

RAM_X4はフレームバッファが2個あります(ピンポンモード)。RAM_X4_WR_SELは1画面(4ライン)ごとにH/Lになり、書き込みアドレスRAM_X4_WR_ADDRは0〜15

-> 0〜15と遷移します。 |

図9‐63 RAM_X4にはフレームバッファが2つある。代わりばんこに書き込む

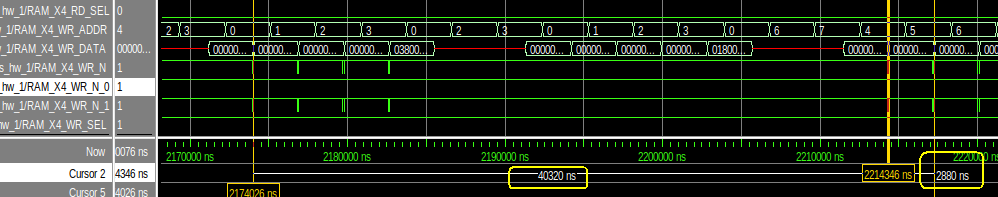

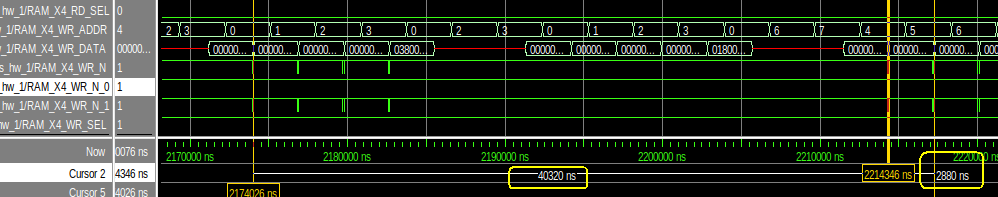

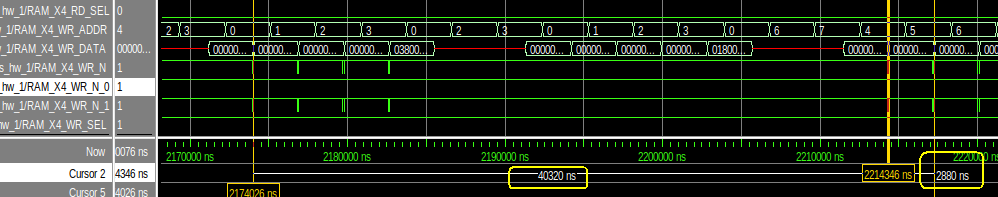

●書き込みタイミングが想定通りになっているか

図9‐64のように1画素書き込むのに2880ns、1ライン(13画素)書き込むのに40.32usかかります。このタイムチャート通りになっているか確認しましょう。 |

図9-64 RAM_X4の書き込みを拡大

最初のページへ

目次へ戻る

|