5‐02 各層間のRAMを考える

●層間のメモリは2種類ある

このブロック図を見ると、画像メモリは4ラインぶん(黄色)と2フレームぶん(水色)の2種類あります。まずは黄色の部分について説明します。

●カーネルサイズが3×3・・・ということは・・・

このボード搭載のFPGA(5CSEMA5F31C6)には約4Mb(500kB)の内部SRAMがあり、それを層間メモリとして使用します。

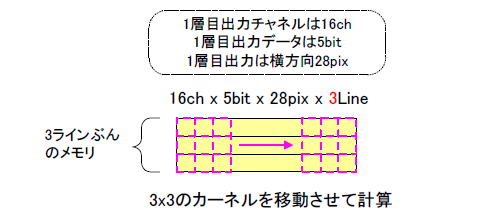

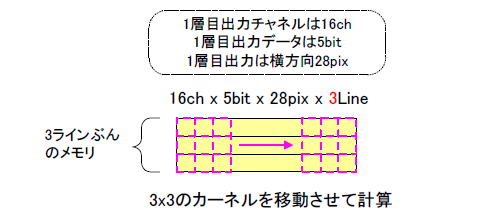

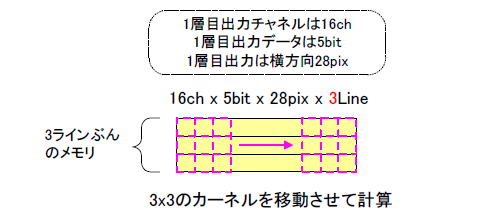

ここで、本企画のCNNのカーネルサイズは3×3だったことを思い出しましょう。それを図5‐04のように横にずらしながら畳み込みを行います。さしあたりは3行ぶんのメモリがあれば十分ということに気が付きます。 |

図5-04 3行ぶんあればどうにかなりそう

●3+1で4ラインぶんあればよい

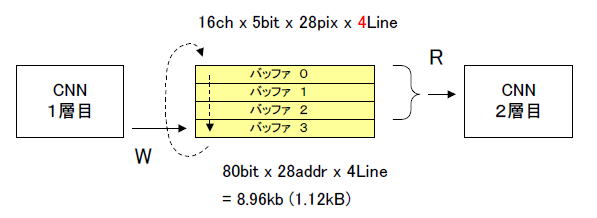

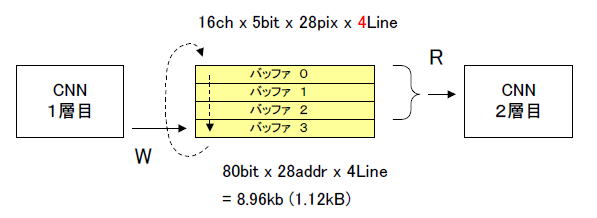

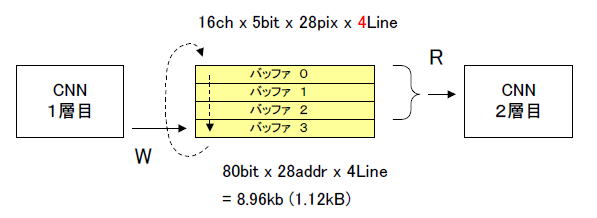

本企画は「リアルタイム画像処理」を目指すので、「書きながら読む」工夫が必要になります。従って実際は図5-05のように1ライン増やして4ラインぶんの画像メモリを設けます。

1層目の出力は16ch、データ幅は5ビット、CNN1ブロックの横一ラインは28画素なので、同図のようにビット幅が80、アドレスが28あるバッファが4つあれば済みます。 |

図5‐05 書き方(W)を追いかける読み方(R)

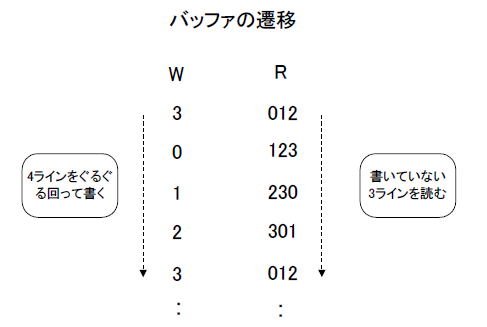

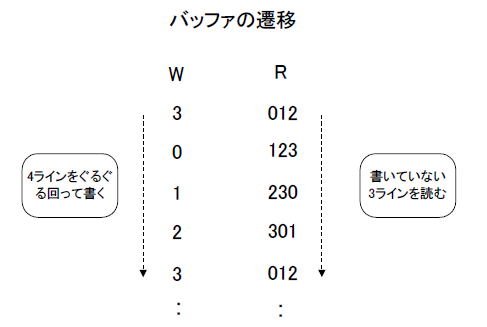

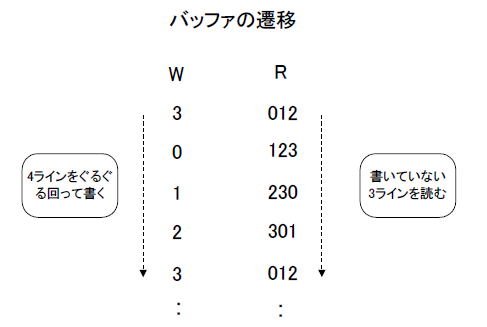

●書いていないバッファを読めば安全に読める

1ラインぶん余分に設けることにより「書きながら読む」ことができます。例えばバッファ3を書いているとき、はバッファ0,1,2を読みます。図5‐06のように書き方(W)を追いかけるように、読み方(R)は書いていない3ラインを読みます。 |

図5‐06 1ライン書く間、書いていない3ラインを読む

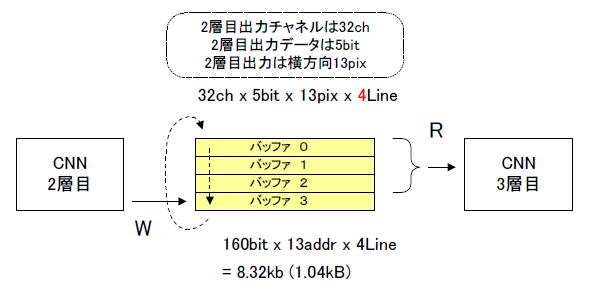

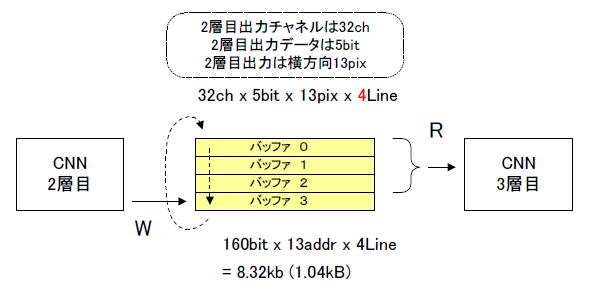

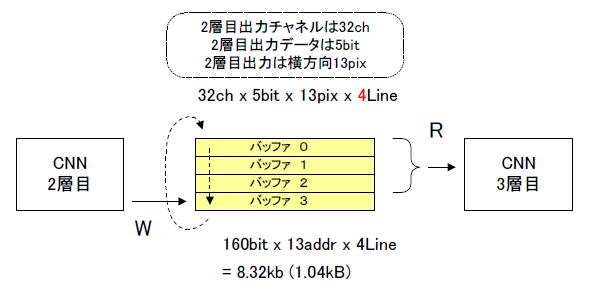

●2層目も同様に4ラインのバッファ

2層目の出力は32ch、データ幅は5ビット、CNN1ブロックの横一ラインは13画素なので、図5‐07のようにビット幅が160、アドレスが13あるバッファが4つあれば済みます。 |

図5‐07 2層目はチャネルが増えるが画素は減る

次のページへ

目次へ戻る

|