10-01 conf-2, 3層目のVHDL化(続き)

●conf-2層目はカーネルが3x3

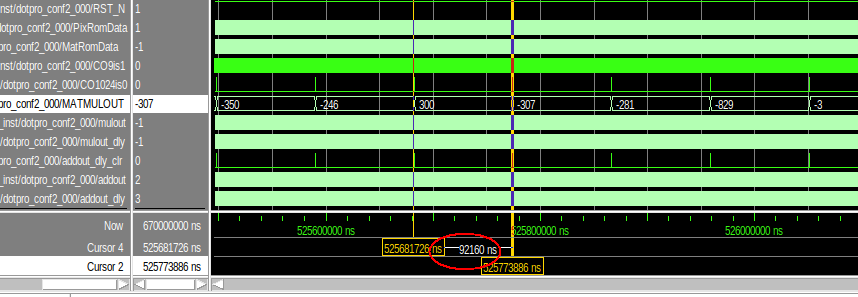

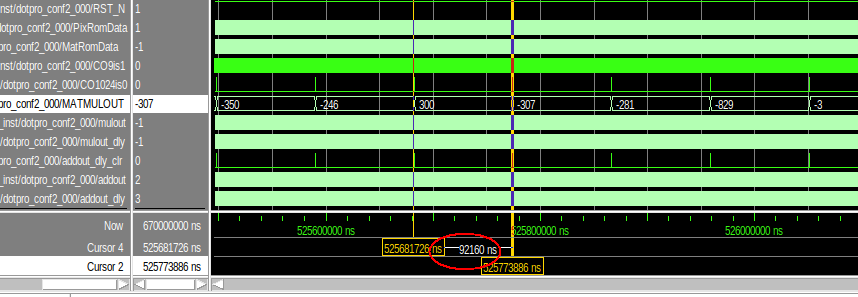

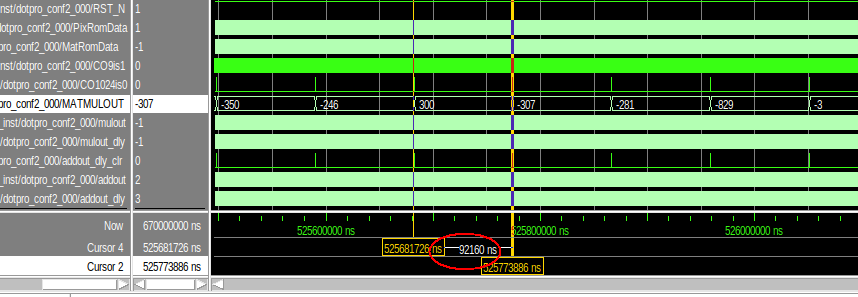

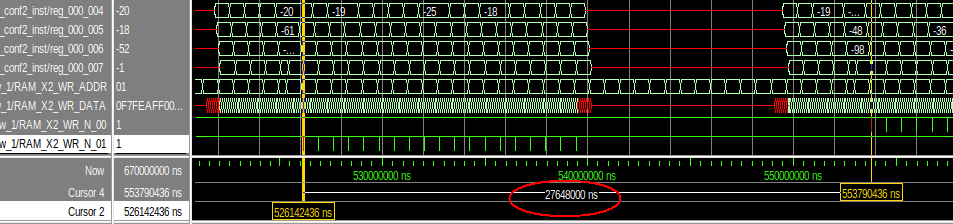

図10-04は積和演算の部分、出力1チャネルの1画素を計算するのに90ns x 1024

= 92160nsかかります(入力1024チャネル、カーネルが3x3なので)。 |

図10-04 入力1024チャネル、カーネル3x3なので92160ns(クロック100MHz)

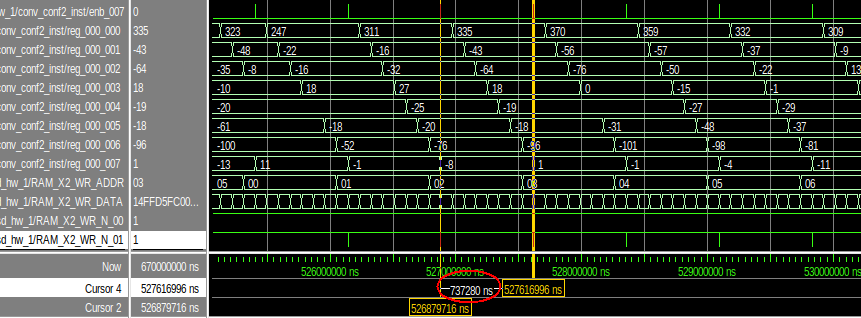

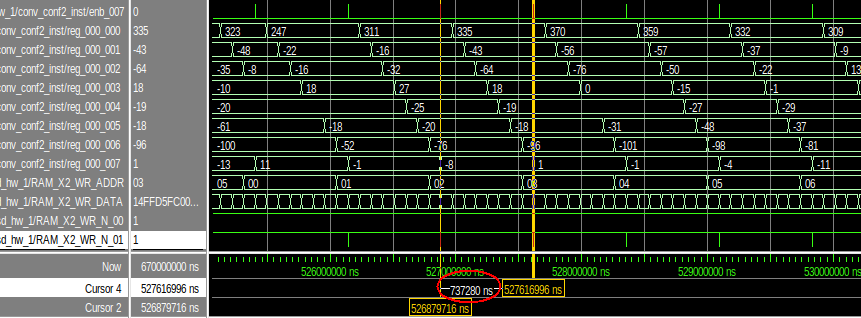

●乗算器を16個並列に動かす

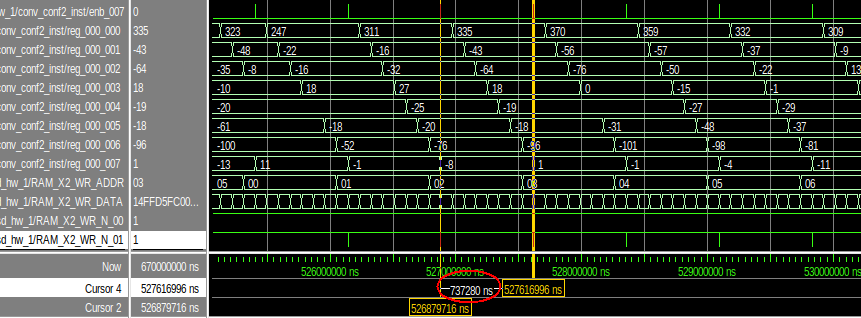

図10-05は一つの乗算器で出力8チャネルの1画素を計算するようす、92160ns

x 8 = 737.28usかかっています。これが16個並列で動くので出力126チャネルの1画素を計算するのに737.28us、19x19画素なので1ラインに737.28us

x 19 = 14.00832msかかります。 |

図10-05 一つの乗算器で8chの出力を計算する

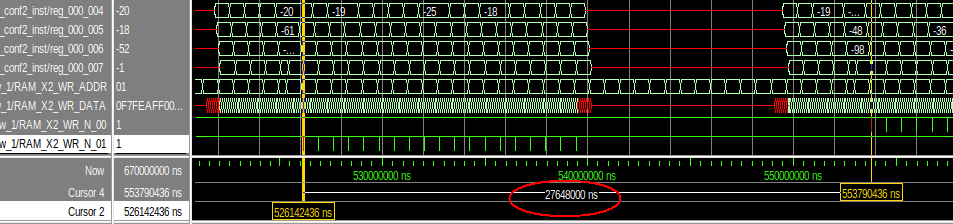

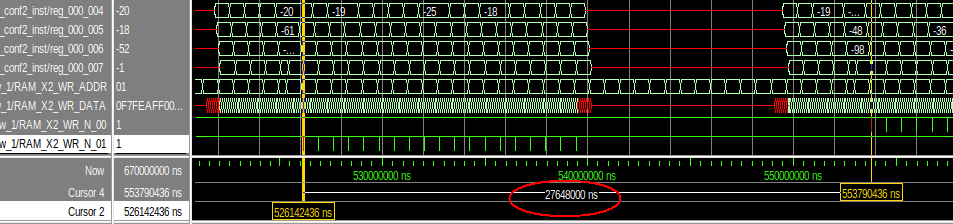

●1ラインはvgg-15層目と同じ

図10-06は1ラインぶん演算して書き込む部分です。周期はvgg-15層と同じ27.648msになります(14.00832ms+休み時間)。また1画面計算するにはその19倍かかります。 |

図10-06 1ライン演算して書き込むようす

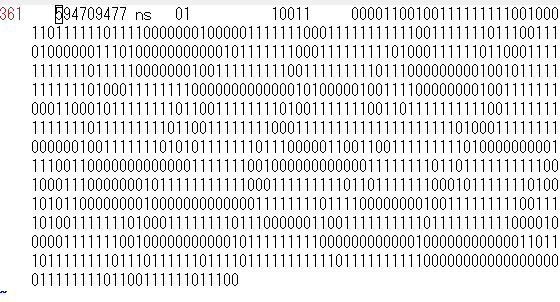

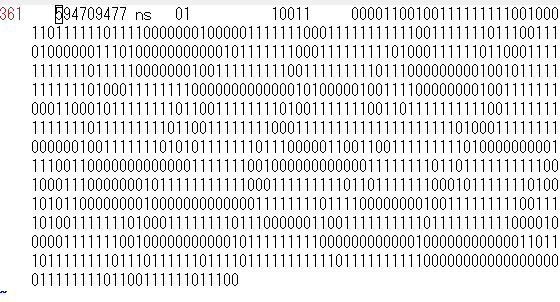

●relu.outに出力が書かれている

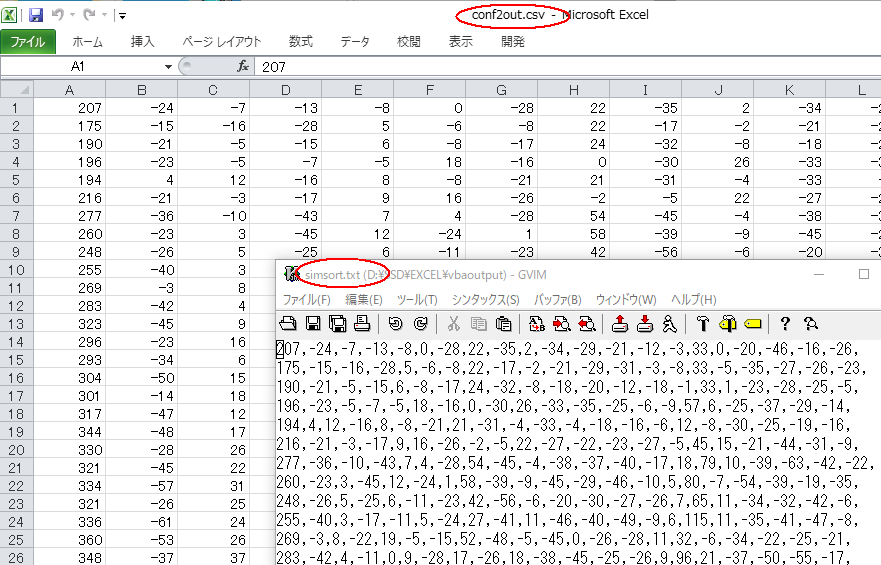

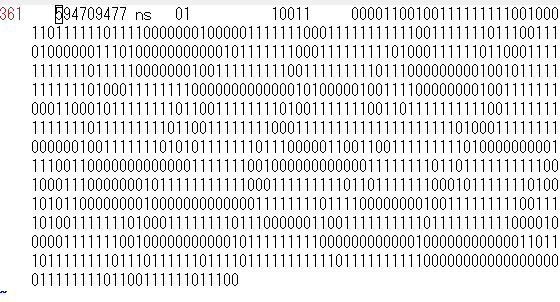

conf-2層目も出力はテキストファイルに落とされます(図10-07)。19×19画素なので1画面で361行、また出力は126チャネルなのでビット幅は

12bit x 126 = 1512bit になります(この層は1画素が符号付き12ビットになる)。 |

図10-07 各画素12ビット、符号付きであることに注意

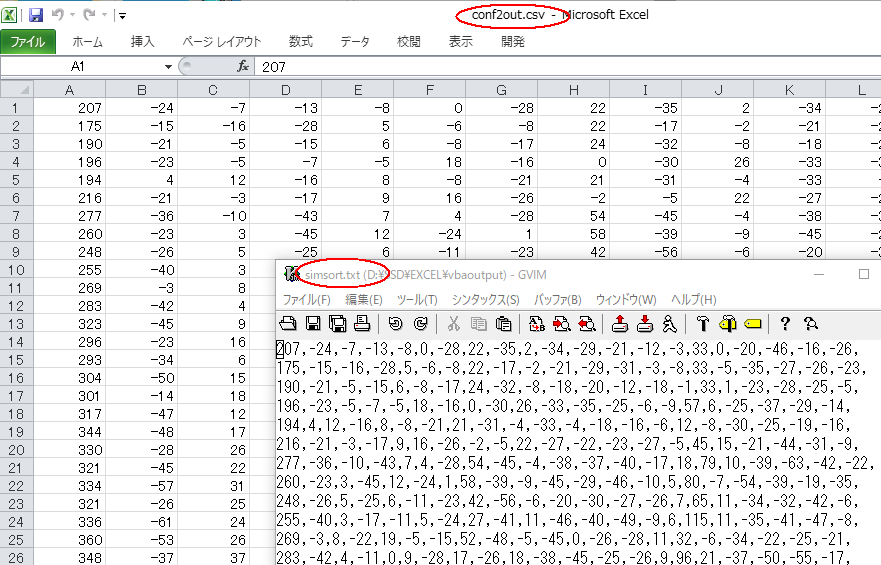

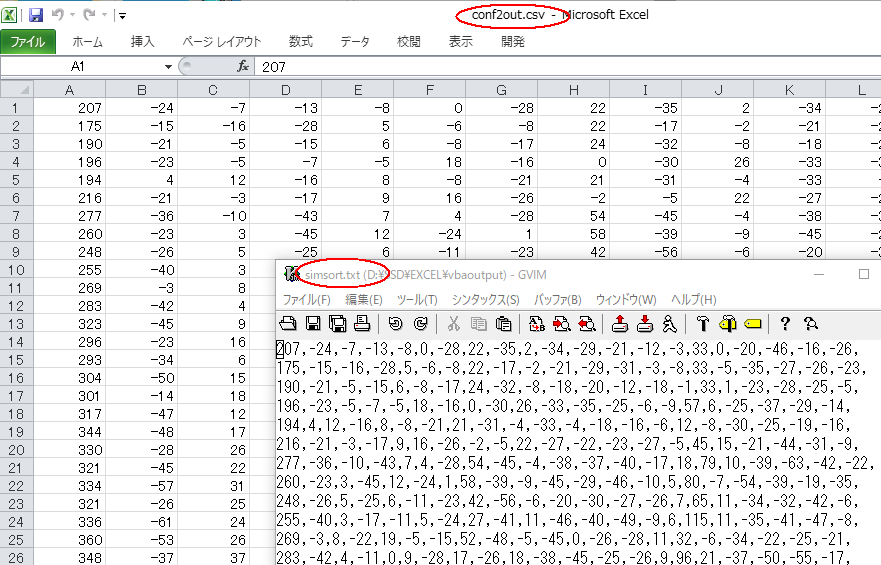

●バッチファイルでデータ並び替え

上図のrelu.outは各行 12bit x 126 = 1512bit ですが、126は21×6であり、21というのは種族(人、馬、自動車、バイクなど)の数、6というのはBBOXの形状の数です。このデータの並びをVBAでこのように21×6列になっているのを21列に並び替えます。

①EXCELファイル(下のリンク)を開く。

②EXCELファイルの場所にvbaoutputフォルダを作成する。

③vbaoutputフォルダにrelu.outをコピーする。

④VBAのModule20, 21を続けて実行する。

⑤vbaoutputフォルダにsimsort.txtが作成される。

⑥simsort.txtとPythonの結果(下のリンク)を比較する。

⑦図10‐08のようにピタリ一致することを確認する。 |

図10‐08 どちらもカンマ区切りなのでファイル比較ソフトで比べるとよい

次のページへ

目次へ戻る |