9-04 extras-7, 8層目のVHDL化(続き)

●extras-7層目はカーネルが1x1

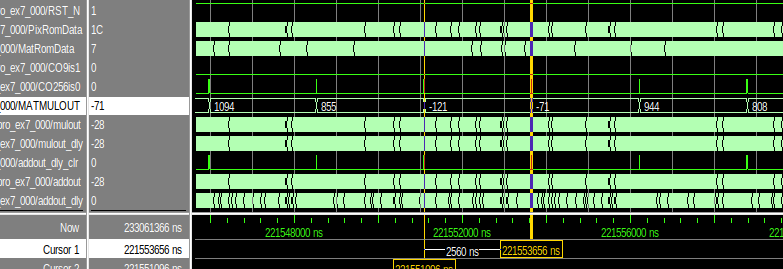

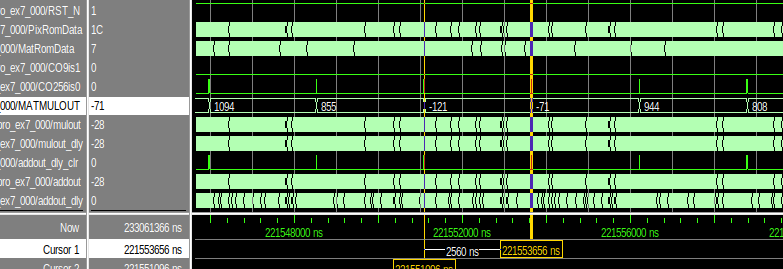

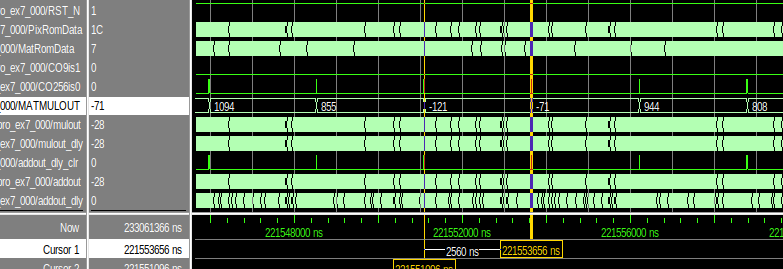

図9-50は積和演算の部分、出力1チャネルの1画素を計算するのに10ns x 256

= 2560nsかかります(入力256チャネル、カーネルが1x1なので)。 |

図9-50 入力256チャネル、カーネル1x1なので2560ns(クロック100MHz)

●カーネルが小さいのでその分たくさんのチャネルを計算できる

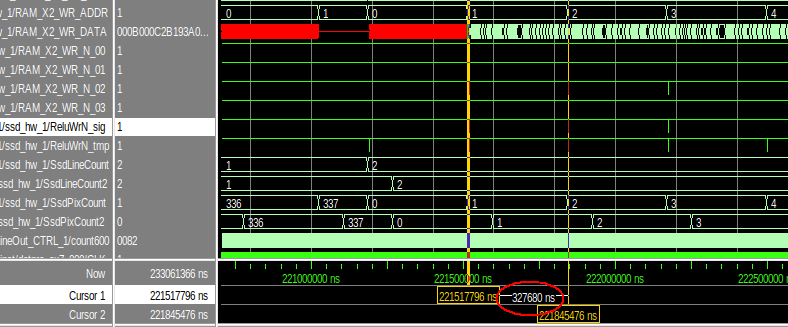

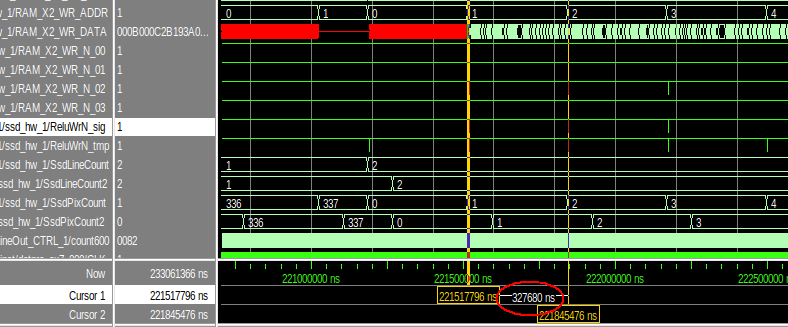

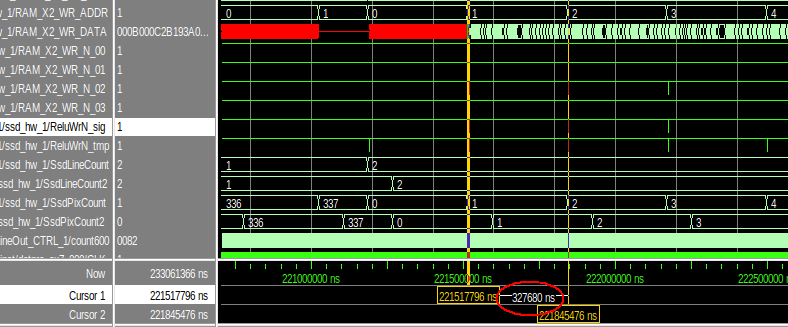

図9-51は一つの乗算器で出力128チャネルの1画素を計算するようす、2560ns

x 128 = 327.68usかかっています。この層は出力が128chなのでこれ1つで十分であり、全チャネルの1画素を計算するのに327.68us、3x3画素なので1ラインに327.68us

x 3 = 0.98304msかかります。 |

図9-51 一つの乗算器で128chの出力を計算する

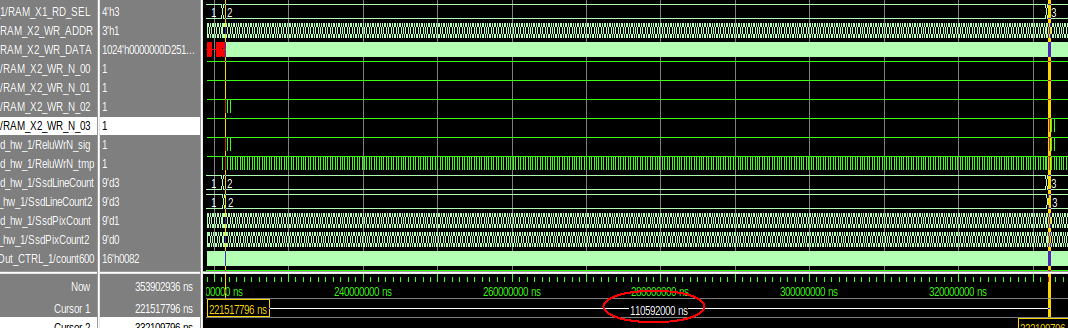

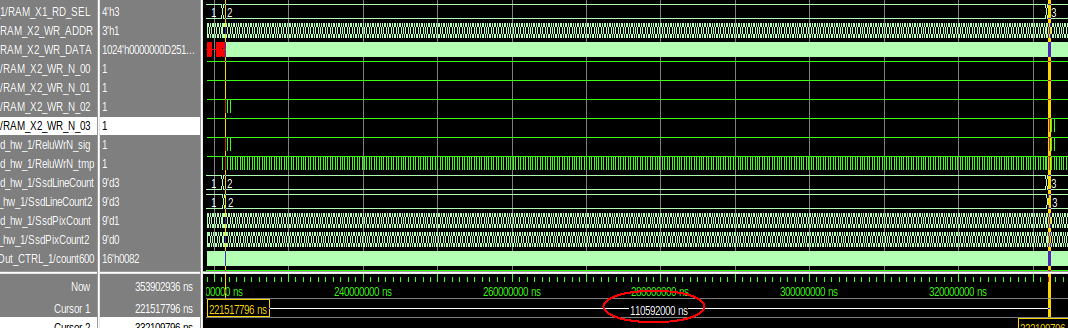

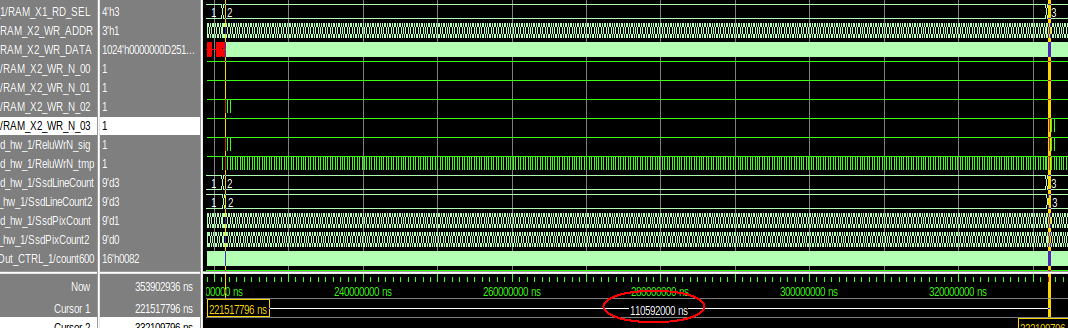

●1ライン3画素書いて後は休み時間

1ライン(3画素)書きこむ周期は図9-52のように110.592msになります。3ラインぶん繰り返して1画面ぶん終了しますが、この後2ラインぶん休み期間を設けて前層と同期をとります。 |

図9-52 1ライン演算して書き込むようす

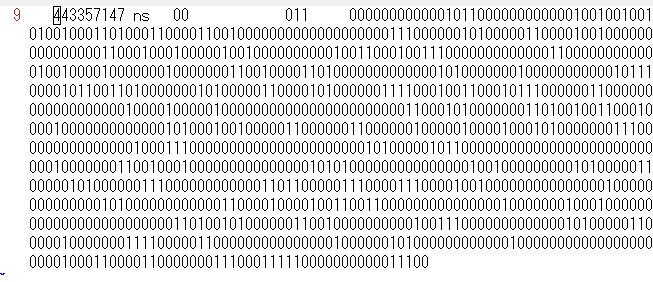

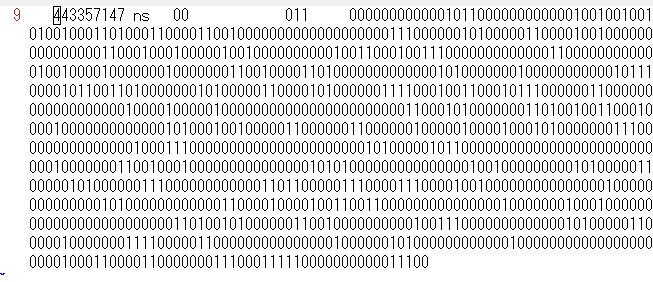

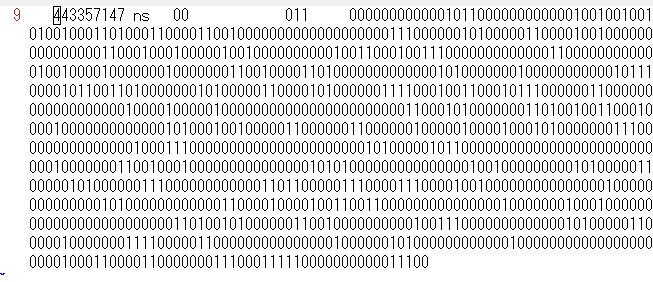

●relu.outに出力が書かれている

extras-7層目も出力はテキストファイルに落とされます(図9-53)。3×3画素なので1画面で9行、また出力は128チャネルなのでビット幅は

8bit x 128 = 1024bit になります(1画素8ビット)。これをVBAで128個のCSVファイルに分割してPythonの結果と比較します。 |

図9-53 各画素8ビットであることに注意

●バッチファイルでまとめて比較する

CSVファイルが128個もあるので、前層までと同様にバッチファイルによって比較し、全てのチャネルがピタリ一致することを確認します。 |

次のページへ

目次へ戻る |