9-04 extras-7, 8層目のVHDL化(続き)

●パディングなし故に画素数が減る

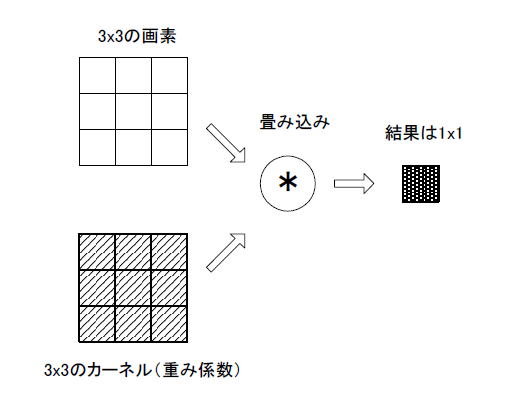

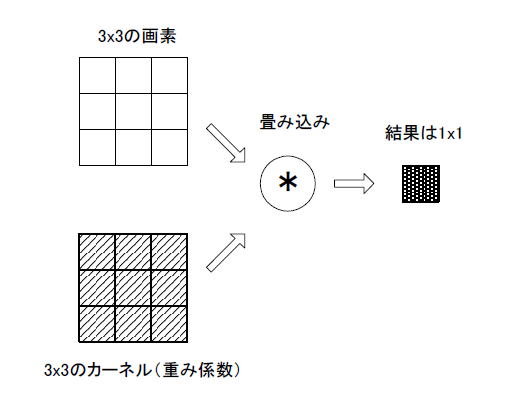

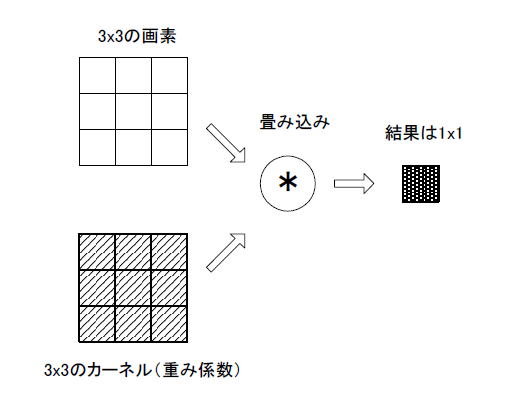

extras-8層目では図9-58のように、3x3の画素と3x3のカーネルを積和演算します。カーネルは動かしようがないので(パディングはなし)、出力は1x1画素になります。 |

図9-58 得られる結果は1x1

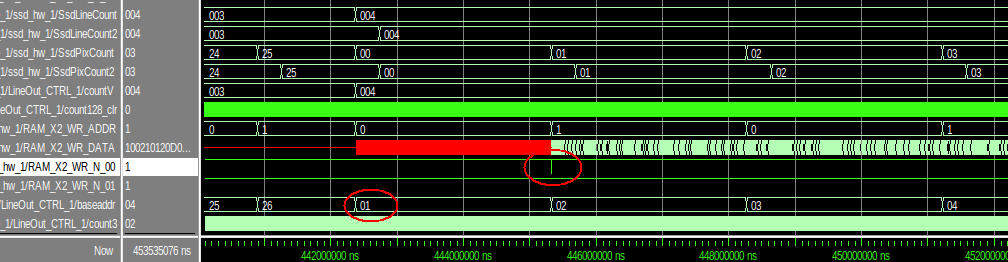

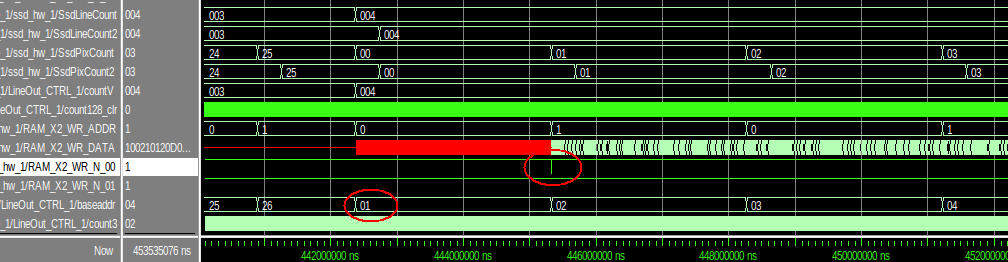

●baseaddr=1のときだけ計算

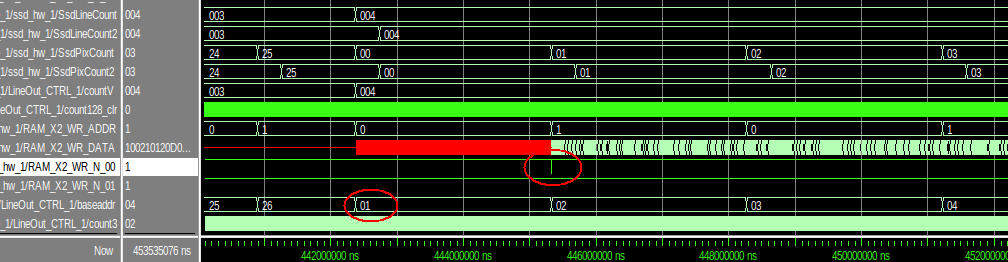

図9-59ではbaseaddr=1の最後の期間だけ出力を書き込んでいます(RAM_X2_WR_N_00

= L)。出力の画素数は1x1なので、1画面での書き込みはこの1画素だけです(チャネル数は256)。 |

図9-59 baseaddrが読み出しアドレスのベースになる

●relu.outに出力が書かれている

extras-8層目も出力はテキストファイルに落とされます(図9-61)。1×1画素なので1画面で1行、また出力は256チャネルなのでビット幅は 8bit x 256= 2048bit になります。これをVBAで256個のCSVファイルに分割してPythonの結果と比較します。 |

図9-61 1x1画素なので1行、8ビットx256chで1行2048ビット

●バッチファイルでまとめて比較する

CSVファイルが256個もあるので、前層までと同様にバッチファイルによって比較し、全てのチャネルがピタリ一致することを確認します。 |

●extras層の結果がconf層に行く

これでextras層は終わり、次はconf層になります(この図の右中段)。conf層で各BBOXの信頼度(*2)を計算してSSD物体認識は終了です。

(*2)そのBBOXにどの種族(人、馬、自動車、バイクなど)が、どれくらいの確度で存在するかを示す値。 |

最初のページへ

目次へ戻る |