8-01 vgg-1層目のVHDL化(続き)

●テストベンチの中に回路本体がある

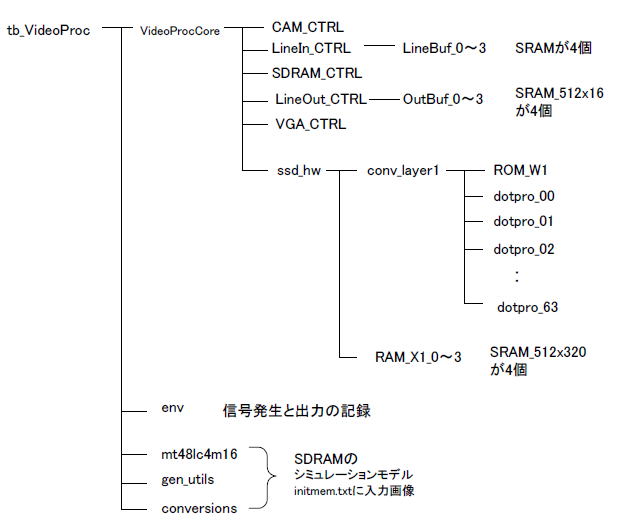

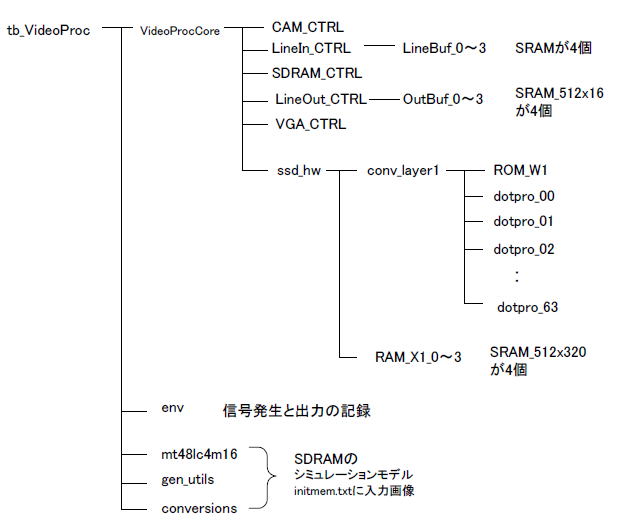

vgg-1層目のModelSim(シミュレータ)プロジェクトのアーカイブを解凍すると図8‐03のような構成になっています。

トップモジュールはtb_VideoProcで、これはVHDLで書かれたテストベンチです。その下にVideoProcCore, env, mt48lc4m16, gen_utils, conversionsがあり、VideoProcCoreが回路本体のトップになります。 |

図8‐03 ModelSimプロジェクトのツリー構造

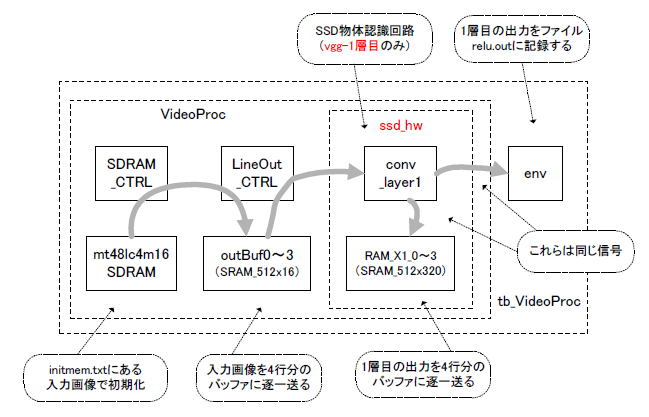

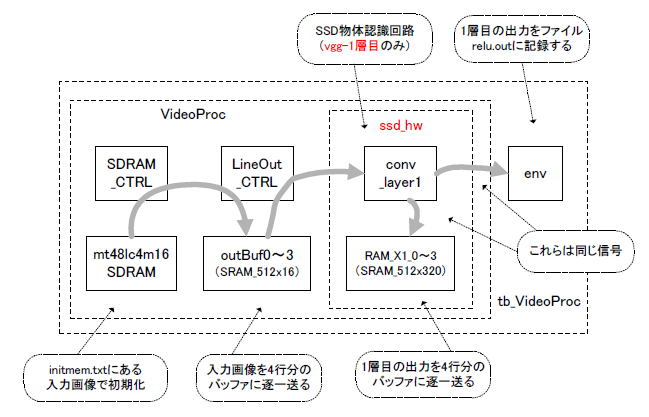

●あらかじめSDRAMに画像を置いてからシム

mt48lc4m16はSDRAMのシミュレーションモデルです(*1)。initmem.txtにある画像データ(この一番上の人と馬の写真)によって初期化されます(*2)。

(*1)FPGA外部にあるSDRAMの動作をビヘイビアレベルで記述したもの。このモジュールは論理合成しない。

(*2)さしあたりCMOSカメラはない状態でシミュレーションする。SDRAMに最初から画像を持たせてそれを認識させる。

SDRAM(FPGA外部)にある画像データは図8‐04のようにSDRAM_CTRL, LineOut_CTRLを経てoutBuf0〜3(FPGA内部メモリ)に送られます。その画像データは認識回路(ssd_hw)に送られますが、さしあたりvgg-1層目(conv_layer1)のみでシミュレーションします。 |

図8‐04 画像データの流れ

●1層目の出力の行き先は2つ

1層目の出力はRAM_X1_0〜3(FPGA内部メモリ)に送られます(*3)。1フレーム全部ため込むのではなく、ここで述べたように4ラインぶんあれば十分です。

(*3)このメモリ内のデータが次層(vgg-2)の入力データになる。出力は1ライン300画素なのでアドレスは512、チャネルは64あるのでビット幅は

5bit x 64 = 320bit になる。

また1層目の出力はenv(シミュレーション用環境ファイル)にも入力され、テキスト形式でファイル(relu.out)に記録されます(*4)。

(*4)このrelu.outとPythonの結果を比較してピタリ合えば成功。 |

次のページへ

目次へ戻る |