7-01 SSDの並列化の限界を探る

●全結合型なら画素数ぶんのサイクルが限界

ここでMNIST(手書き文字)認識をハードウェア化しましたが、「第1部 全結合ニューラルネットワークのハードウエア化」では並列化・パイプライン化により、このように画像1枚当たり「1.1kサイクル」で推論できました。

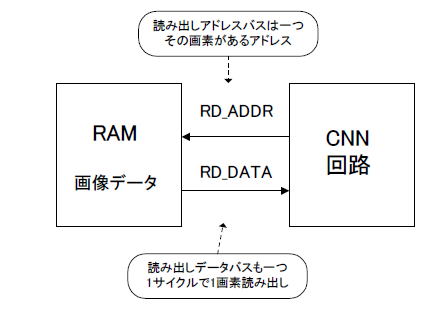

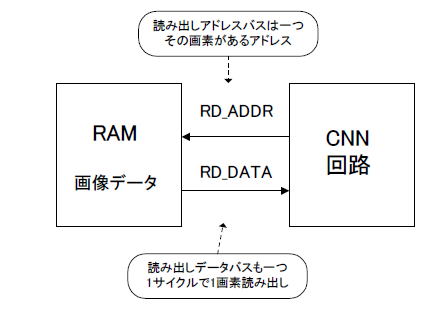

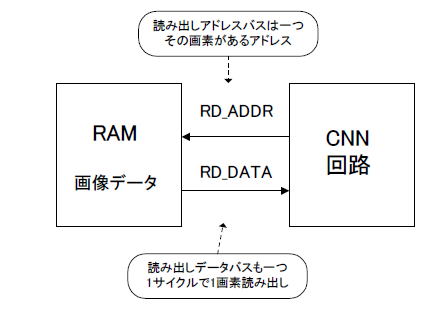

MNIST画像は28×28=784画素なので、全結合型の場合、この"784"がサイクル数の下限になります。なぜかと言うとFPGAのようなハードウエアにおいて画像は"RAM"に置かれます。通常その「読み出しポート」は一つしかなく(図7-01)、1サイクルで1つのアドレスしかアクセスできません。(*1)

(*1)RAMではなくDF/F(D型フリップフロップ)のようなレジスタに画像を置くと回路規模が爆発的に増える。

「1サイクルで1画素しか取り出せない」という宿命があるため、どんなに並列化しても画素数(784)サイクルを下回ることができず、結果的に上記のように784+αの「1.1kサイクル」になりました。 |

図7-01 RAMの読み出しポートは一つしかない

●畳み込み型なら画素数×9サイクルが限界

ここの「第2部 畳み込みニューラルネットワーク(CNN)のハードウエア化」で並列化した際のサイクル数は、このように画像1枚当たり「9.8kサイクル」で推論できました。

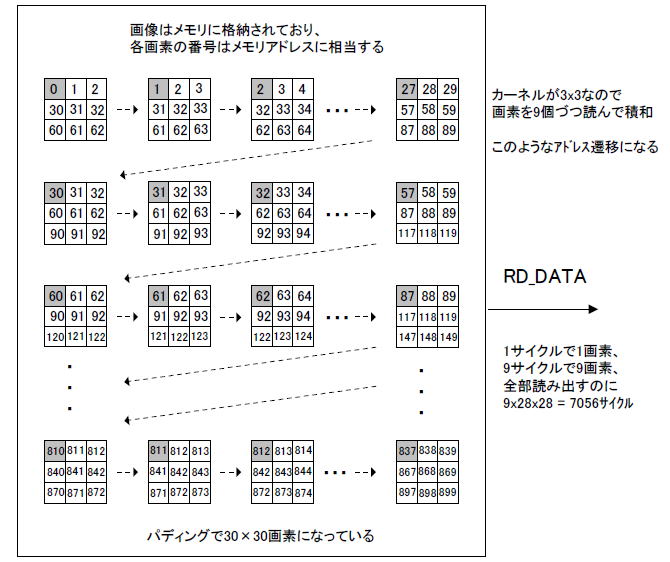

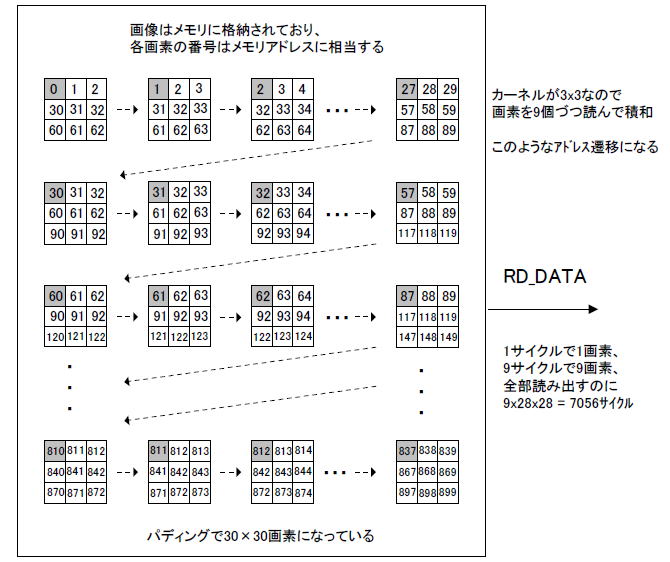

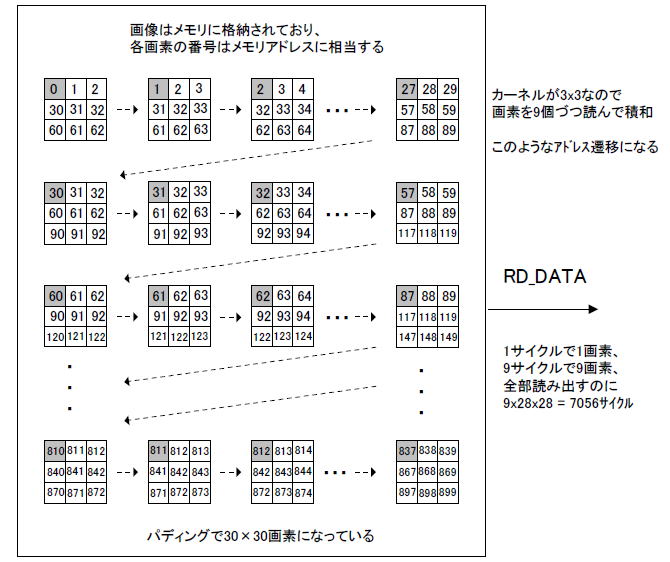

このCNNにおいてカーネル(2次元フィルタ)は3×3でした。係数が9個あるのでそれらに対応する9画素を読み出して乗算します(図7-02)。CNNでも同様に画像はRAMに置かれるため、1回のフィルタ演算(積和)にどうしても9サイクルかかります。(*2)

(*2)画像RAMを9個設けて同じ画像を置けば1サイクルで9画素が得られるが、回路規模的に非効率である。

畳み込み演算の場合この9回のフィルタ乗算を画素数(784)ぶん行います。したがってCNNの場合、784×9=7056がサイクルの下限になり、結果的に上記のように7056+αの9.8kサイクルになりました。 |

図7-02 CNNだと画素数×9倍のサイクルかかる

●SSDの画素数はMNISTの100倍!

SSD物体認識の入力画素数は300×300あります(ここの左上)。MNIST(784画素)の100倍以上(90,000画素)あるのでサイクル数も100倍以上になります。SSDもCNNなので90,000

x 9 = 810,000サイクルが下限になり、最大限並列化しても+αで900kサイクル程度になりそうです。 |

次のページへ

目次へ戻る |