15-03 lisa-cropped ロジックアナライザで内部信号を見る

●パソコンからFPGA内部をのぞいてみる

lisa-cropped(信号機の認識)ではまずPythonを変更、その後EXCELを変更してVBAでHDL生成、最後にそれらHDLをコピーしてFPGAにプログラムしました。

ここではFPGAの内部信号をロジックアナライザで観測し、PythonやEXCELと演算結果を比較します。このサイトに倣ってSignalTapをスタートし、設定しましょう。

●PythonやExcelと同じ画像をFPGAに入力する

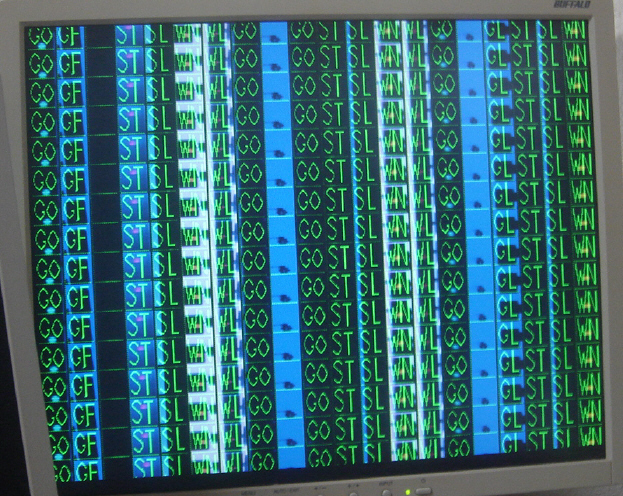

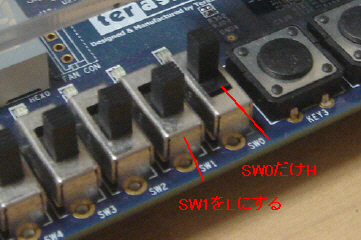

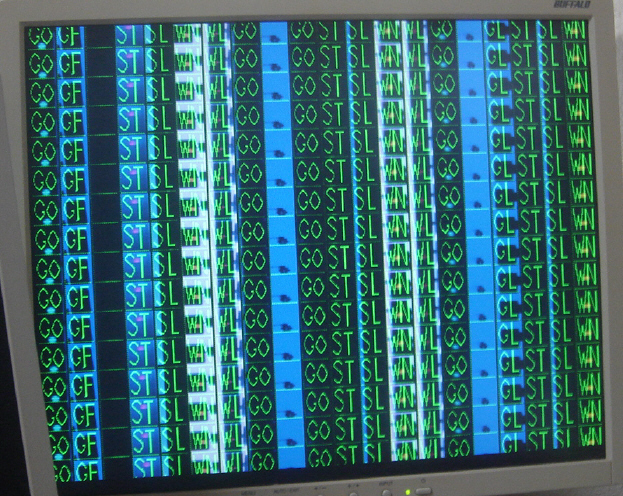

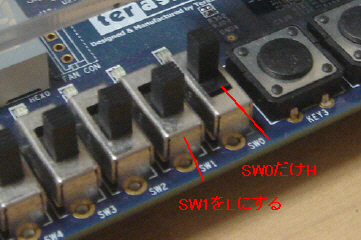

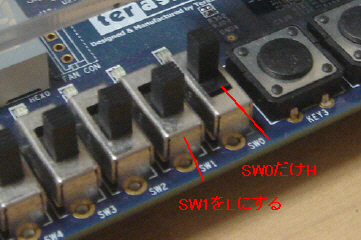

図15‐27(a)はカメラエミュレータモードで、lisa-croppedのテスト画像がカメラ動画の代わりに入力されます(同図(b)のように設定)。この状態でロジックアナライザをRunします。 |

(a) (a)

(b) (b)

図15‐27 lisa-croppedのテスト画像を入力して判定するモード

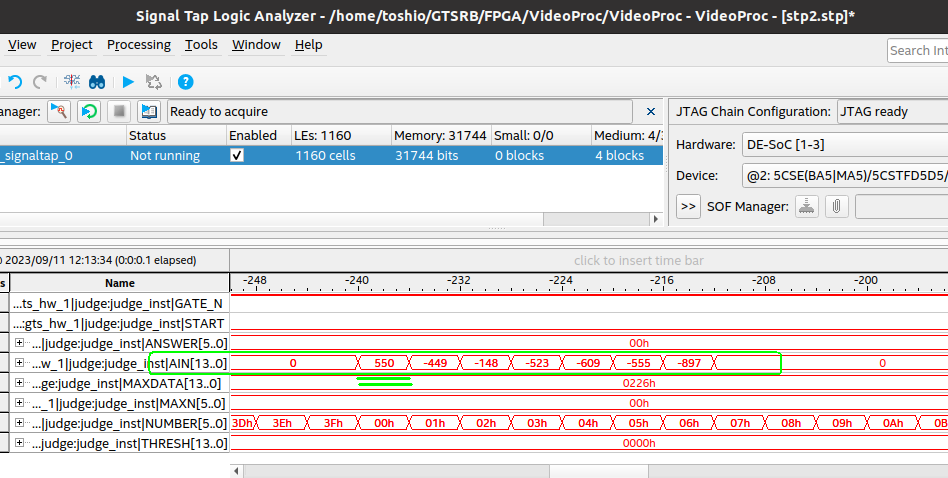

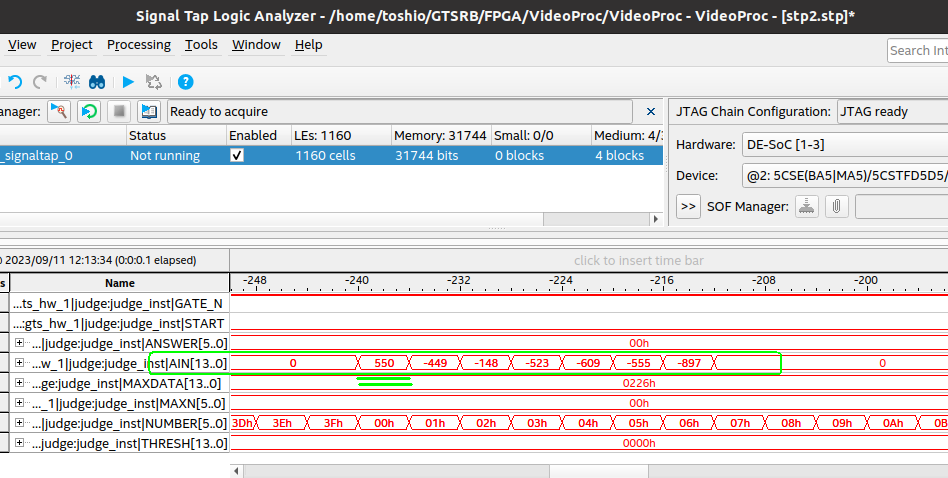

●FPGA内部での判定のようすが分かる

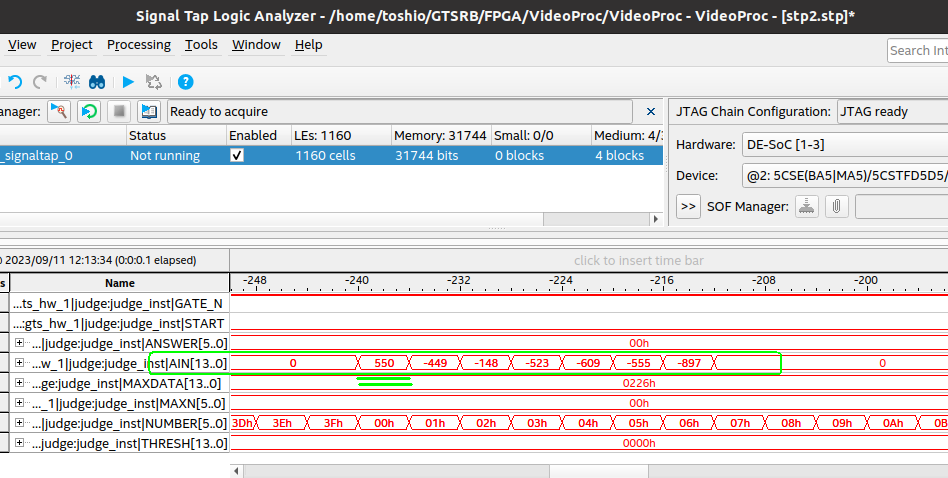

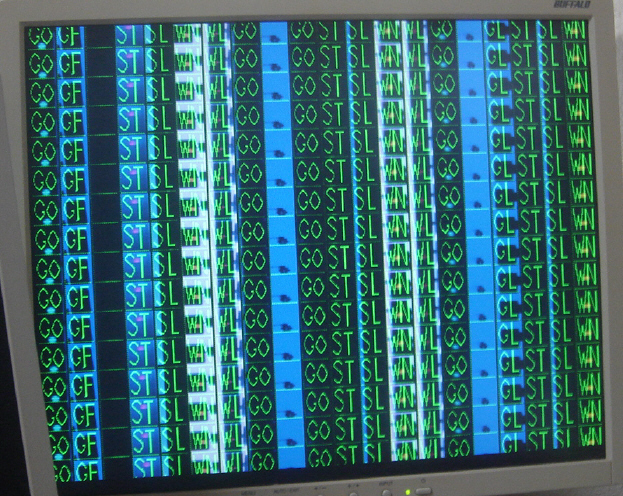

図15‐28はSignalTapの画面、judge(判定回路)の信号です。AINを見ると 550, -449, -148, -523, -609, -555, -897と続きます。lisa-croppedの場合、クラスが7個なのでこの信号も7つの値が出てきます。このうち最大のものは"550"、0番目なので答えは0 (GO, 青・直進)になります。 |

図15‐28 550だけ正の数。ほかは負の数

●EXCELでの演算はどうだったか

図15‐29はEXCELで計算した結果です(lisa_dense56.xlsm)。上図のロジックアナライザとピタリ一致しています。 |

図15‐29 これも550が最大、答えは0

●Pythonとも一致する

図15‐30はPythonが書き出した6層目の出力(lay6out_sample_00.csv)です。ロジックアナライザとピタリ一致していることが確認できます。 |

図15‐30 lisa-croppedの最初の画像の最終層の出力

●整数の掛け算と足し算なので必ず一致する

Python/Excel/FPGA内部信号が一致したということは、Pythonのプログラムが正しくハードウエア化されたことを意味します。

一致しない場合はEXCELなどの途中経過(1層目の出力など)と比較すれば、どこから間違っているかが分かります。

また「論理シミュレーション」はデバグの一手法として強力です。これをlisa-cropped用に変更して走らせるとよいと思います。 |

目次へ戻る

|

(a)

(a) (b)

(b)

(a)

(a) (b)

(b)